RoboCube

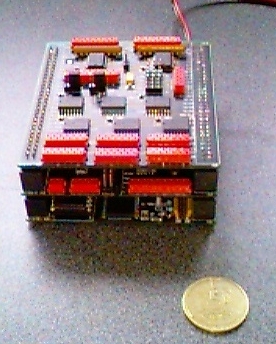

The Robocube has been designed from 1997-2000 at the VUB AI Lab by Dr. Thomas Walle

It is currently used by some research groups including the RIDS (Roboter in der Schule) project and the IUB Robotics group

Robocube's Operating System ''CubeOS'' can be found here

Main features

- open bus architecture

- MC68332 CPU running at 16MHz

- 256kB SRAM main memory

- 128kB EPROM

- 24 analog/digital (A/D) converter,

- 6 digital/analog (D/A) converter,

- 16 binary Input/Output (binI/O),

- 5 binary Inputs,

- 10 timer channels (TPC),

- 3 DC-motor controller with pulse-accumulation (PAC), and

- an intelligent active InfraRed (aIR) subsystem.

RoboCube Version 2.0

Currently, we are working on a new version of the RoboCube platform. New features include:- BDM interface

- Embedding of DUART and I2C

- DRAM and FPU extension

The embedding of the DUART and the two I2C busmaster chips allows a much higher CPU frequency, i.e. 25MHz. Additionally, 16 direct memory mapped binary outputs could be inserted.

On top of that, an additional board was designed. It hosts a MC68882 FPU chip running at 25MHz and implements 16MB of DRAM. Since the whole physical address space is 16MB, only 13MB are accessible.

Again, the pdf sources of the used components can be retrieved here and the schematics can be seen here.