## CUBEOS A COMPONENT-BASED OPERATING SYSTEM FOR AUTONOMOUS SYSTEMS

HOLGER KENN Artificial Intelligence Laboratory Vrije Universiteit Brussel

August 2001

## CUBEOS

## A COMPONENT-BASED OPERATING SYSTEM FOR AUTONOMOUS SYSTEMS

### HOLGER KENN Artificial Intelligence Laboratory Vrije Universiteit Brussel

### PROEFSCHRIFT VOORGELEGD VOOR HET BEHALEN VAN DE ACADEMISCHE GRAAD VAN DOCTOR IN DE WETENSCHAPPEN, IN HET OPENBAAR TE VERDEDIGEN OP 27 AUGUSTUS 2001

### **Promotiecommissie:**

| PROMOTOR:      | Prof. dr. L. Steels, Vrije Universiteit Brussel          |

|----------------|----------------------------------------------------------|

| VOORZITTER:    | Prof. dr. D. Vermeir, Vrije Universiteit Brussel         |

| SECRETARIS :   | Prof. dr. A. Birk, Vrije Universiteit Brussel            |

| OVERIGE LEDEN: | PROF. DR. KURT MEHLHORN, MPI FÜR INFORMATIK, SAARBRÜCKEN |

|                | Dr. H. Bruyninckx, Katholieke Universiteit Leuven        |

|                | Prof. dr. H. Sahli, Vrije Universiteit Brussel           |

# Acknowledgments

First, I want to thank my advisors. Andreas Birk gave me the opportunity to work with him in an international environment on the topic of autonomous systems and artificial intelligence although I had not worked in this area before. During my time in his research group, I could complete my knowledge in computer architecture and system software engineering and I learned many new and interesting things from the research on the origins of intelligence. Also, I am very grateful for the opportunity to work with Luc Steels in his AI Lab. Although I am not directly involved in his research on the origins of language, I had many fruitful discussions with him and with other members of the lab over related topics and again, I learned a lot.

Also, I want to thank Prof. Dr. Kurt Mehlhorn and Dr. Ir. Herman Bruyninckx who agreed to act as external members of the Ph.D. committee and to the VUB members of the committee, Prof. D. Vermeir and Prof. Dr. H. Sahlim.

Thanks to the other members of the lab, Tony Belpaeme, Joachim De Beule, Karina Bergen, Edwin De Jong, Joris Van Looveren, Dominique Osier, Paul Vogt, Jelle Zuidema and especially to Thomas Walle with whom I had endless discussions over various aspects of Hard- and Software. Although I could rarely convince him of my views, I did learn a lot from him.

Also, I thank all the beta-testers of CubeOS, the students and the researchers from other universities and the people at Quadrox N. V. and ProSign GmbH that looked at my code and told me where the bugs were.

I also like to thank my parents, Anni and Wolfgang Kenn for supporting me, not only financially, but for giving me the mental support necessary to survive a Ph.D. I also like to thank the people at the MPI für Informatik, espechially at the Computer Service Group for showing me that there is a practical side to computer science and supporting me in various projects. Last but not least, I'd like to thank Heiko Kamp and Oliver Kohlbacher for staying in touch with me while we're all spread over the world.

# Contents

| Α                    | Acknowledgments     v |        |                                                         | V  |

|----------------------|-----------------------|--------|---------------------------------------------------------|----|

| A                    | Abstract xi           |        |                                                         | xi |

| Ir                   | Introduction xv       |        |                                                         | XV |

| 1 Autonomous Systems |                       |        |                                                         |    |

|                      | 1.1                   | Design | n of autonomous systems                                 | 3  |

|                      |                       | 1.1.1  | Software-design techniques                              | 3  |

|                      |                       | 1.1.2  | Realtime design techniques                              | 4  |

|                      |                       | 1.1.3  | Robot design                                            | 6  |

|                      | 1.2                   | Impler | nentation of autonomous systems                         | 9  |

|                      |                       | 1.2.1  | Computational hardware                                  | 10 |

|                      |                       | 1.2.2  | Programming language for system software implementation | 11 |

|                      | 1.3                   | Operat | ting system services for autonomous systems             | 11 |

|                      |                       | 1.3.1  | Multithreading                                          | 13 |

|                      |                       | 1.3.2  | Scheduling repetitive tasks                             | 20 |

|                      |                       | 1.3.3  | Inter-thread communication and synchronization          | 31 |

|                      |                       | 1.3.4  | Mutexes, spin-locks and semaphores                      | 33 |

|                      |                       | 1.3.5  | Priority inversion                                      | 36 |

|   |     | 1.3.6            | direct hardware access                     | 38 |  |

|---|-----|------------------|--------------------------------------------|----|--|

|   |     | 1.3.7            | realtime clock                             | 39 |  |

|   |     | 1.3.8            | initialization and configuration           | 42 |  |

|   | 1.4 | Comm             | unication services for autonomous systems  | 43 |  |

|   |     | 1.4.1            | wireless communication                     | 44 |  |

|   |     | 1.4.2            | modulation and data encoding               | 45 |  |

|   |     | 1.4.3            | Media Access Methods                       | 45 |  |

|   |     | 1.4.4            | high-level data encoding                   | 46 |  |

|   | 1.5 | Conclu           | usion                                      | 47 |  |

|   |     |                  |                                            |    |  |

| 2 | Ope | rating s         | ystem design                               | 49 |  |

|   | 2.1 | Operat           | ing Systems                                | 49 |  |

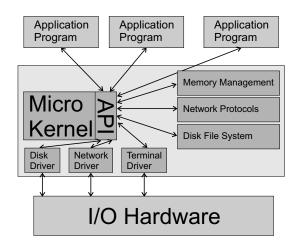

|   |     | 2.1.1            | Monolithic kernel operating systems        | 50 |  |

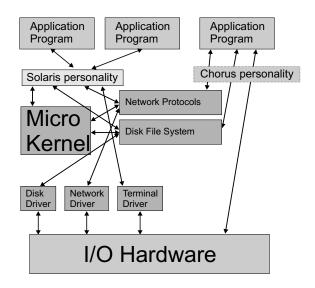

|   |     | 2.1.2            | Micro-kernel and modular operating systems | 53 |  |

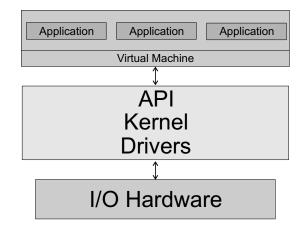

|   |     | 2.1.3            | Nanokernels and virtual machines           | 55 |  |

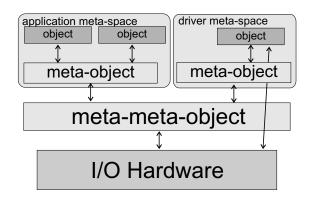

|   |     | 2.1.4            | object oriented operating systems          | 56 |  |

|   |     | 2.1.5            | component operating systems                | 57 |  |

|   |     | 2.1.6            | Realtime operating systems                 | 59 |  |

|   |     | 2.1.7            | Exception handling                         | 60 |  |

|   | 2.2 | Conclu           | usion                                      | 63 |  |

| 2 | The | Cuba             | C Vormal                                   | (5 |  |

| 3 |     | CubeOS Kernel 65 |                                            |    |  |

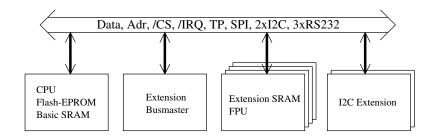

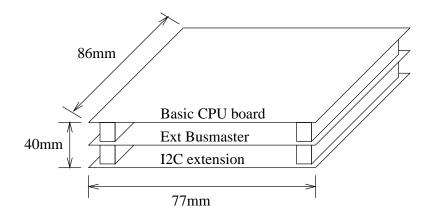

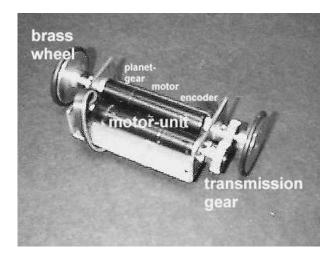

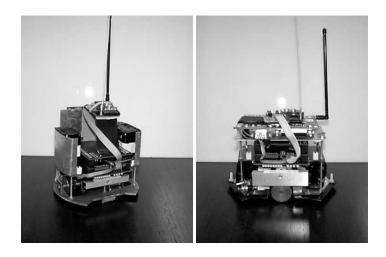

|   | 3.1 | Hardw            | are: The RoboCube                          | 65 |  |

|   |     | 3.1.1            | CPU                                        | 66 |  |

|   |     | 3.1.2            | System                                     | 67 |  |

|   |     | 3.1.3            | Busses                                     | 70 |  |

|   |     | 3.1.4    | i/o interfaces                                                          |

|---|-----|----------|-------------------------------------------------------------------------|

|   |     | 3.1.5    | intelligent devices                                                     |

|   |     | 3.1.6    | boot monitor                                                            |

|   | 3.2 | Softwa   | are Environment                                                         |

|   |     | 3.2.1    | Details of the C language implementation of GCC for the RoboCube<br>CPU |

|   | 3.3 | The gl   | obal design of RoboCube                                                 |

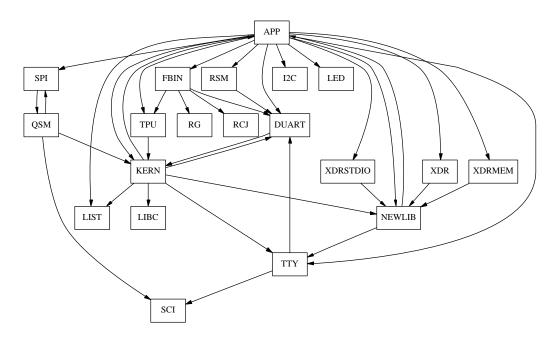

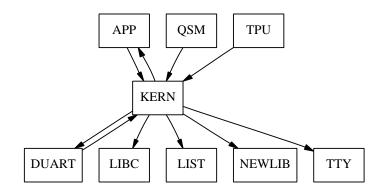

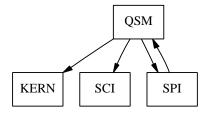

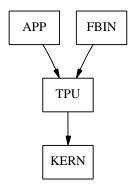

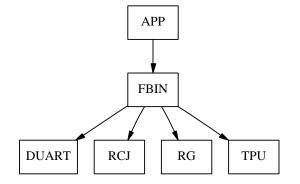

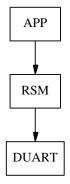

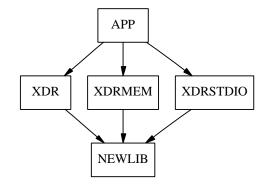

|   |     | 3.3.1    | CubeOS components                                                       |

|   | 3.4 | Detaile  | ed aspects of the implementation                                        |

|   |     | 3.4.1    | System configuration                                                    |

|   |     | 3.4.2    | Abstract datastructures                                                 |

|   |     | 3.4.3    | Interrupt service routine implementation                                |

|   |     | 3.4.4    | The multi-threading scheduler and context switch implementation 87      |

|   |     | 3.4.5    | time delay and communication i/o                                        |

|   |     | 3.4.6    | semaphores and priority inversion avoidance                             |

|   |     | 3.4.7    | exception processing and recovery                                       |

| 4 | Арр | lication | of CubeOS 99                                                            |

|   | 4.1 | reusab   | le components: RobLib                                                   |

|   | 4.2 | interpr  | eter for visual control block architecture: icon-L                      |

|   | 4.3 | semi-a   | utonomous architecture: RoboGuard                                       |

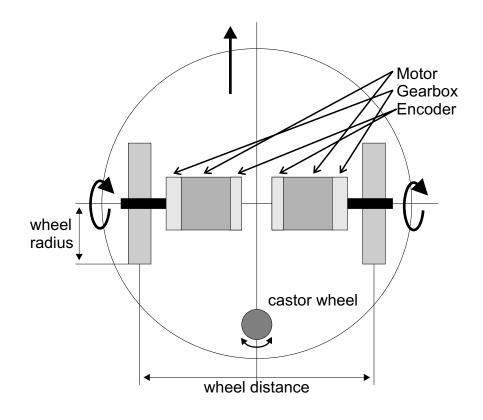

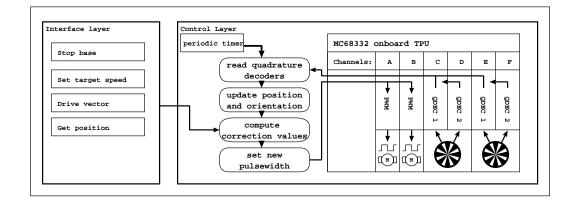

|   |     | 4.3.1    | Components and Integration of the Mobile Base                           |

|   |     | 4.3.2    | The Control Software                                                    |

|   |     | 4.3.3    | RoboCube Software Drivers and Operating System Support 108              |

|   |     | 4.3.4    | The Strategic and Path-Planning Layers                                  |

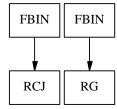

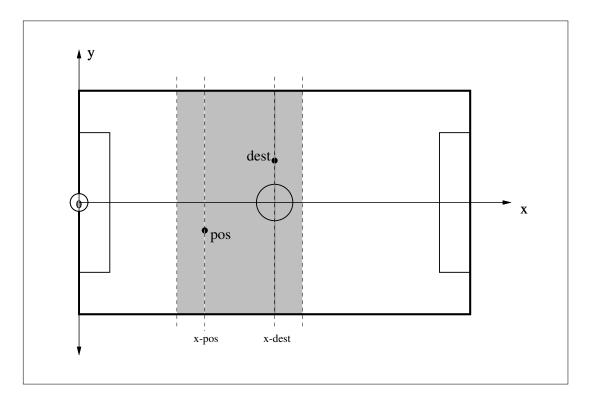

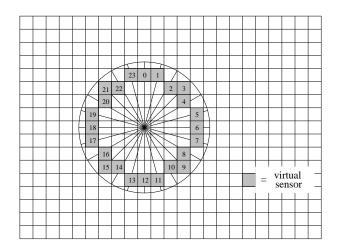

|   | 4.4 | distrib  | uted architecture: RoboCup                                              |

|     | 4.4.1 | Classification of Team-Approaches          |

|-----|-------|--------------------------------------------|

|     | 4.4.2 | Towards a Robot Construction-Kit           |

|     | 4.4.3 | Using the RoboCube for Highlevel Control   |

| 4.5 | Advan | ced behavior-oriented architecture: NewPDL |

|     | 4.5.1 | The Process Description Language (PDL)     |

|     | 4.5.2 | simulation of a nPDL system for debugging  |

|     | 4.5.3 | postmortem analysis of a running program   |

## Abstract

In this thesis, research about software design for autonomous systems is presented. A component-based operating system has been designed that has many special features which support the rapid development of autonomous systems for various applications.

These special features are:

- a new scheduler for simple control tasks that optimizes the regular execution over wide timespans,

- drivers for various common sensors and actuators,

- an efficient implementation of general-purpose operating system services that respects the limited hardware resources on autonomous systems,

- and support for high-level components for various common problems, e.g. a component to control differentially-driven mobile robots.

This operating system, CubeOS has been implemented from scratch for the so-called RoboCube, a newly-designed embedded control computer based on the Motorola MC68332 MCU.

CubeOS and the RoboCube have been successfully used in various applications ranging from teaching and various research applications to an industry project.

# Introduction

As with most other open-source projects, the initial reason to start CubeOS was frustration over the available software. It occurred after completing the design phase of the RoboCube[BKW98] hardware architecture which is a modular embedded controller for autonomous systems. There was no adequate operating system that could make use of the unique modularity of the new hardware. Moreover, there was a wide field of possible applications for the new architecture, ranging from teaching over industrial applications[BK01b] to experiments about multi-robot cooperation[McF94, Ste94] and the emergence of language[Vog98]. A stable operating system is a requirement for all these applications. Unfortunately, neither available open-source nor commercial implementation would perfectly fit.

The drawback of the commercial operating systems are that every developer needs a separate development license which is quite expensive. Although there were special reductions for academic use, these academic licenses could not be used in the context of an industry project. Another drawback was the focus on traditional embedded and realtime applications in which a system is once designed from specifications and is then mass-produced. This contradicts the approach found in the academic environment, where an operating system is used as the basis for multiple software environments such as nPDL[BKS00] on top of which different application programs are implemented.

From the available open-source operating systems, most of them did only support widelyavailable hardware such as PCs. Even systems that did support hardware similar to the RoboCube were lacking all the special functions such as the modularity that were needed for our applications. Moreover, many open-source operating system projects suffer from poor design, poor documentation and "featurism". There were some exceptions, e.g. RTEMS[RTE] and eCos[eCo] but unfortunately, RTEMS was too much focussed on classic realtime approaches and eCos does not support the CPU architecture of the RoboCube.

From this, it was decided to design and implement a new operating system for autonomous systems.

Designing an operating system for autonomous systems led to some unique challenges that were not adressed in existing systems. One of them was scheduling repetitive executions. Conventional schedulers for general-purpose operating systems rely on the fact that most of the time, the system is i/o bound, i.e. the system is either waiting for user interaction or for an i/o operation to complete. By sorting the tasks according to a fixed or dynamic priority value and running the highest-priority non-blocking task, these systems can acchieve good overall system performance. However, the way autonomous systems are designed leads to the situation that there is not such a high amount of idle time in higher priority tasks, therefore, lower priority tasks would hardly be run.

To overcome this situation, a novel type of scheduler has been designed that guarantees execution frequency ratios between tasks of different priority.

The unique modularity and the huge ammount of different hardware devices involved in the physical design of autonomous systems make the design process of an autonomous system a complex task. Therefore, the operating system should support the user and add as few complexity to the design task as possible. As a consequence CubeOS has been designed as a component system in which the designer of an autonomous system can construct an operating system that exactly fits the autonomous system that it is constructed for. Only the components needed are included, others are left out automatically and the designer can implement additional components if necessary.

## **Chapter 1**

## **Autonomous Systems**

In this chapter, the general design considerations for the CubeOS operating system are presented that result from the application domain of autonomous systems. From this, a list of necessary operating system services is compiled and presented in detail.

According to [Bir01], an autonomous system is a combination of:

- a computational core

- network connections

- sensing and effecting subsystems

- a finite resources store

- a guiding control

What are the requirements for an operating system for an autonomous system?

First of all, an autonomous system has to act more or less without external supervision for extended periods of time. So the operating system should also require as few maintenance as possible. Moreover, it should be highly *stable* since it cannot rely on a human operator as last resort. In the event of a failure, the system should either recover from it (failure-tolerant, "self-healing") or bring everything to a safe state so that no further damage results.

The resources of an autonomous system are constrained. One example is electrical power, another one is size and weight. As a result, the on-board computer of the autonomous system is constrained in computation power and memory. An operating system for autonomous system should therefore be as *efficient* as possible to leave as many resources as possible to the application program. Another important aspect is that the guiding control of an autonomous system has to deal with complex situations. Therefore, the design goal for the implementer of such a system is to make it able to work under these complex circumstances, usually resulting in a rather complex system design. The operating system should reduce the complexity of this task. For that, the operating system should be *simple* and should work in a *transparent* way.

Many parts of the system are only used for specific applications, e.g. driver software is only used if the corresponding hardware is present in the system. Therefore, the operating system should be designed in a *modular* way and the implementer should be able to *customize* it, so that it provides the functions necessary for the application but nothing more.

One field where this customization is very important is the domain of *sensors* and *actuators*. The operating system should contain functions to access various kinds of these devices with the option to add more that are specific to the application.

An important task of an autonomous system is the reaction to the world around it in a timely manner. Therefore, the operating system has to provide functionality to deal with *real time* events and *timing constraints*.

In the following sections, these requirements are inspected in detail and various approaches of their implementation are discussed.

A example for an autonomous system is a mobile robot operating independently in a unstructured environment. This will be the standard example of an autonomous system throughout the next chapters although many other classes of autonomous systems are possible. However, the mobile robot is a good example since it includes all features of an autonomous system and is useful to present the common problems of autonomous system design.

- A mobile robot has a finite resource store, i.e. limited onboard batteries.

- It has a small onboard computer for control.

- Most mobile robots have some mean of communication, either with an operator or other mobile robots.

- It has onboard sensors, i.e. distance sensors or bump switches.

- It has onboard actuators, at least to move the robot itself, often also additional manipulators.

Mobile robots of this type are often used in academic research. Some applications are presented in Chapter 4.

### **1.1 Design of autonomous systems**

To analyze the requirements for an operating system for autonomous systems, design techniques for autonomous systems are reviewed and from this, the necessary features of the operating system are derived. There are no design techniques that are specific to autonomous systems. However, the design of an autonomous system can benefit from design techniques in various related fields.

#### **1.1.1** Software-design techniques

There are various software design techniques that can be applied to autonomous systems, such as object-oriented programming (as in [Mur00]) or software component technology[Szy99]. For the system software, *software components* have been selected as the main design paradigm. Software components have a strong support for modularity which is one of the key requirements. Within the components, various other design techniques and even different programming languages can be applied such as object-oriented design, simple procedural or even functional programming as long as there is a clearly-defined interface for these components. From this results a minimal restriction for the implementer in flexibility and extendibility of the system. More on this topic will be presented in Chapter 2 where the different approaches to operating system design are discussed.

**Definition 1.** [Szy99]: A software component is a unit of composition with contractually specified interfaces and explicit context dependencies only. A software component can be deployed independently and is subject to composition by third parties.

A Software Component has three characteristic properties:

- A component is a unit of independent deployment.

- A component is a unit of third-party composition.

- A component has no *persistent* state.

Components are a well-established concept in other engineering disciplines. In the following section, the term component refers to a software component unless mentioned otherwise. To be independently deployable, a component needs to be well separated from its environment and from other components through encapsulation of its inner workings. For a component to be composable by third parties, it needs to be sufficiently self-contained. Also, it needs to come with clear specifications of what it requires and provides. In other words, a component needs to encapsulate its implementation and interact with its environment through well-defined interfaces. If a component does not have a persistent state, multiple copies of it cannot be distinguished when loaded (as it is possible, i.e., with objects). Therefore, there is no need to

load multiple copies of a component. Although it makes sense to ask whether a component is available, it is not meaningful to talk about the number of available copies of that component [Szy99]. In many current approaches, components are heavyweight units with exactly one instance in a system, such as a database server. If that database server maintains only one database, then it is easy to confuse the instance with the concept. In this case the database server is a component, but the module formed by the database and the database server is not. The situation becomes clearer if there are two databases served by that same database server. There is no need to load a second instance of the server to make both databases available. As will be shown later on, components can be used in a much-more lightweight way in the composition of small embedded software systems. But the main concept stays the same: Although a software component may service several instances of data (or external devices) it is only present once in a system.

A component system needs to define two main functions: The way components are composed, i.e. linked into a system and the way the interfaces between two components are specified by the designer and used by other components. By specifying a component system, one has to specify the *contracts* between components. Such a contract is a more or less formal specification of the interface(s) of a component and some aspects of its implementation. This specification does not only include what e.g. a call to a function will do, but also additional information like execution time, resource usage and possible error codes returned. These contracts must be specified as clearly as possible to simplify object composition by users. One possible way to specify such a contract is by giving pre- and postconditions. The caller has to establish the precondition before calling and the caller can rely on the postcondition being met when the call returns.

#### **1.1.2 Realtime design techniques**

When a computational system interacts with the physical world through sensors and actuators, the results of this process do not only depend of the results of the computation but also on the time when sensors are evaluated or actuators are set. Depending on the task that such a system has to fulfill, various timing constraints can be derived. For a simple fire alarm system, such a constraint might be that the fire alarm has to be triggered no later than 5 seconds after a fire has been detected by a smoke sensor. From this, the following definition describes a realtime system:

**Definition 2.** [rea]: A realtime system is one in which the correctness of the computations not only depends upon the logical correctness of the computation, but also upon the time at which the result is produced. If the timing constraints of the system are not met, system failure is said to have occurred.

Realtime system design tries to predict whether a computation within a system is completed at the right time. This requires usually a great deal of knowledge about a computer system and the software running on it. Realtime theory assumes that on such a system, there are multiple

#### 1.1. DESIGN OF AUTONOMOUS SYSTEMS

software modules, called *tasks*. These tasks are related to external events, they receive input and give output to the external world. Tasks can either be *sporadic* or *cyclic*. Sporadic tasks have to react to an external event, cyclic tasks have a *period* after which they are re-run. For both types of tasks, timing constraints are given in the form of *deadlines* which are points in time at which the result of the computation has to be present. In the example with the fire alarm, a sporadic task triggered by the smoke detector must not take longer than 5 seconds to trigger the alarm, even if interrupted by other tasks with possibly higher priority. Alternatively, a cyclic task checking the smoke detector that is run every 3 seconds may not take longer than 2 seconds to do this. On the other hand, it is also necessary to know a great deal about the world surrounding the realtime system since it defines the timing constraints for the system and therefore the deadlines for the various tasks. Deriving these realtime constraints from the environment is a challenge on its own and it is often much harder than in the fire alarm example. But Realtime system design assumes that these constraints are readily available.

For realtime systems, there are various approaches known that can decide a priori whether a system can meet all its deadlines. [LL73] [ABRW91] Most of these approaches deal either with sporadic or cyclic tasks. But fortunately in a cyclic task system, a sporadic task can be modeled as a cyclic task checking whether its external event has occurred and its period has to be less than the deadline of the sporadic event minus the time it takes to compute the result. Therefore, it is sufficient to analyze periodic tasks. If the system can meet all deadlines, a static schedule can be constructed that will meet all timing constraints, e.g. by rate-monotonic analysis[LL73].

The drawback of all these approaches is that they assume all timing constraints to be known a priori and to be stable over the runtime of the system, otherwise the deadlines cannot be specified. Another frequent drawback of static schedules is their inefficiency since they have to provide enough computational resources for the worst case. On the other hand, if the worst case happens (and if it exceeds the one that was foreseen in the deadline specification) static schedules react inflexible to failures and overloads[BPB<sup>+</sup>98]. To overcome the first problem, mode-based scheduling was introduced. It assumes that a system is operating in different kinds of environments, such as a car driving on dry or on wet roads. For each of these modes, a different static schedule can be computed. For the car driving on a wet road, the anti-lock brake task deadline may be reduced and therefore, the deadline for the air conditioner temperature controller may be enlarged. This leads to better service qualities through better resource usage in all modes.

To be able to react better to overloads or failures, dynamic realtime scheduling based on *values* was introduced[JLT86]. Here, the system can dynamically reschedule. Its decisions are based upon *value functions* that model the current *utility* of a task being executed now. In the event of an overload, the tasks with the lowest value can be dropped to provide additional resources for other tasks. However, the value function is just a heuristic for the utility of a task. Computing a dynamic schedule (with the computation of the schedule taken into account) at runtime is a NP-hard problem [CM96].

### 1.1.3 Robot design

The most common implementation of an autonomous system is a mobile robot. In this section, an overview is given over various approaches for designing mobile robots. Most robots used in research today are using a mixture of these design approaches and since one design goal for the system software is flexibility, they should all be supported.But first, a criterion to compare the different approaches is necessary.

According to [Ark98], robotic architecture is the discipline devoted to the design of highly specific and individual robots from a collection of common software building blocks. Note that in the context of robotic control, the robotic architecture only refers to the software architecture of the robot, not hardware architecture.Robotic architectures are often evaluated on the basis of the following criteria for a good architecture[Ark98]:

- Modularity: Can the architecture be decomposed into modules that can be implemented and tested individually, are inter-module interfaces properly defined, is the architecture based on sound software engineering principles?

- Targetability: Can the architecture be adopted to the intended target problem?

- Portability: Can the architecture be re-used on different robotic hardwares and in different operating environments?

- Robustness: Is the system vulnerable to failures? What are these vulnerabilities? Can they be avoided or reduced in practice?

#### Special-purpose hardware

Historically, one of the first occurrences of a technical robotic design problem was in the context of cybernetics. One of the first theoretical designs was the "Machina Speculatrix by W. Grey Walter [Wal50] which was implemented in hardware in form of Walter's tortoise. It was a mobile robot with one directed light sensor and two motors, one controlling the direction of the movement and of the light sensor, the other moving the robot forward.

The tortoise exhibited the following behaviors:

- Seeking light: The tortoises sensor rotates until a weak light source is detected.

- Head towards a weak light: As long as the weak light source is detected, move towards it.

- Back off from a bright light: Back away if the light is too bright.

- Turn and Push: To avoid obstacles, this behavior overrides the light-related behaviors

#### 1.1. DESIGN OF AUTONOMOUS SYSTEMS

• Recharge battery: This behavior was an intended side effect of the implementation. When the on-board battery power is low, a strong light source is perceived to be weak. The charging station was marked by a bright light. When the on-board battery power is low, the tortoise perceives this light as low and move towards it, docking into the charging station. After the battery is charged again, the light is again perceived as strong and the tortoise backs off.

Although the tortoise does not employ any software (and since it is no robotic architecture in the specific sense) it is an interesting example of the features (like restricted resources, sensors and actuators) and for the problems that occur while designing a mobile robot.

This example illustrates several important features of robotic architectures. First of all, the system is decomposed into several sub-systems. These are defined independently of each other first. Then, the relationship between them is defined, i.e. the "Turn and Push" sub-system "blocks" the "Seeking light", "Head towards a weak light" and "Back off from bright light" subsystems. And last, there are sub-systems that only exist as a side effect of other sub-systems and the implementation environment. Although they are present in the system and are planned, they do not have an implementation of their own.

Applying the criteria for robotic architectures, the tortoise violates some of them. It is a monolithic hardware system whose operating parameters are deeply embedded and not easily modified. Although the hardware system as a whole can be used in other architectures, it's hardly portable to other tasks. But still, the tortoise is a very efficient implementation that fulfills its task with minimal hardware resources.

#### **Hierarchical architectures**

Another approach for robotic architecture are hierarchical architectures, mostly based on classical AI techniques such as symbolic representation of knowledge [Alb91]. The knowledge is stored in a global memory that is accessible to all layers of the hierarchy. Each layer of the hierarchy is separated into sensory processing, world modeling, task decomposition and value judgment. This architecture was standardized in the form of the NASA/NIST(NBS) standard reference model for Telerobot Control System Architecture (NASREM)[AL87] in 1987. This standard is used for example to implement a telerobotic service for maintenance and simple assembly of the NASA Space Station.

NASREM defines six hierarchical levels which each capture a specific functionality.

- 1. Servo: provides servo control for the robot's actuators, i.e. position and force control

- 2. Primitive: motion primitives, smooth trajectories

- 3. Elemental move: path-planing of robot movements, collision-avoidance

- 4. Task: Converts a desired action into sequences of elemental moves to accomplish the action.

- 5. Service bay: converts actions on groups of objects to actions on the individual members of the group and schedules these tasks.

- 6. Service mission: Decomposes the overall mission plan into service bay commands.

Each of the levels consists of a sensory processing component, a world model component and a task decomposition component that all have access to a global memory. Each layer's sensory processing component takes input from the corresponding component of the layer underneath, the lowest layer is directly connected to the sensors. The task decomposition components are connected in a similar way where the output of each component is fed into the input of the corresponding component on the layer underneath and the lowest layer task decomposition component is connected to the actuators.

According to the evaluation criteria, this architecture does better. It is clearly structured, it can easily be adopted to many targets, by exchanging sub-modules it can be ported to other applications and hardwares.

Hierarchical robotic architectures are well suited for structured and highly predictable environments, e.g. factory automation systems. However, if the system has to operate in a unstructured, unpredictable environment, hierarchical architectures often fail because of the so-called closed world assumption, stating that every aspect of the world has been stored in the knowledge base of the system. But a different architecture approach can be used instead[Bro91].

#### **Reactive systems**

The class of robotic architectures that is especially well suited to deal with unstructured environments are the so-called reactive systems. According to [Ark98], reactive control is a technique for tightly coupling perception and action, typically in the context of motor behaviors, to produce timely robotic response in dynamic and unstructured worlds.

In the context of reactive systems, a number of terms is often used.

- An individual *behavior* is a stimulus/response pair for a given environmental setting that is modulated by attention and determined by intention.

- *Attention* prioritizes tasks, focuses sensory resources and is determined by the current environmental setting

- *Intention* determines which set of behaviors should be active based on the robotic agent's internal goals and objectives.

- *Emergent behavior* is the global behavior of the robotic agent as a consequence of the interaction of the active individual behaviors.

- *Reflexive* or *purely reactive* behavior is generated by hardwired individual behaviors with tight couplings between sensors and actuators, where sensory information is not persistent and no world models are used whatsoever.

The subsumption architecture[Bro86] by Rodney Brooks is an example of a reactive architecture which only relies on purely reactive behaviors. Others are e.g. motor schemas[Ark87] by R.C. Arkin.

## **1.2 Implementation of autonomous systems**

The actual implementation of an autonomous system includes various sub-problems, from mechanical manufacturing problems of housings and actuators to control software implementation. Although this thesis focuses on software, various aspects of the underlying mechanisms have to be taken into account, among others the computational hardware and the programming language chosen for the implementation. For the onboard computer, the choices are limited through the size- and energy restrictions of the system. Therefore, system software of the onboard computer plays a critical role in the overall performance since it has to work with limited resources.

A general purpose operating system, i.e. for a PC or a server has to offer multiple generalpurpose services such as a user interface, storage management, multi-tasking and others. On a computer running such an operating system, multiple application programs can be executed, from word-processing software to database servers, often in parallel. The designer of the operating system and the hardware manufacturer often do not know the application for which a computer is intended. Over the lifetime of a computer, this application may change, various hardware components are replaced, i.e. hard disks, network interfaces etc., either because they fail or because they become obsolete, new application software is installed and old software is removed. Although these replacements often require a complete re-initialization and re-configuration of the operating system, it is often the case that these re-configurations happen automatically without any need for a new operating-system installation. These features are bought at the cost of a high amount of external storage.

In contrast to this, an autonomous system is a special-purpose hardware-software co-design. This means that the implementor has a certain task in mind that the autonomous system has to fulfill. The autonomous system is designed to exactly execute this task. It is equipped with the appropriate computational and other hardware (sensors, actuators, energy storage, housing etc.) and application- and system software. Over the operating time of the autonomous system, neither hard- nor software is supposed to change, however both are constantly monitored for failures and the autonomous system should be able to recover from this.

From this, the choice of a general-purpose operating system for equipping an autonomous system seems inappropriate. This thesis is going to show how the system software for autonomous systems can be designed and demonstrate this with the actual implementation of CubeOS.

#### **1.2.1** Computational hardware

To be able to specify system software, the computational environment has to be defined for which the system software is intended. This is first done in an abstract way. Later on, an explicit example, the so-called Cube System is used for the actual implementation.

An autonomous system has limited hardware resources through the restriction of energy and space. Therefore, a restricted computational core is mostly found:

- one CPU

- simple CPU architecture (often no cache, limited pipelines)

- often no secondary storage

- restricted communication bandwidth

- restricted CPU clock-speed

- restricted main memory

Unlike standard computers, the computational core may contain additional features:

- multiple hardware interfaces for sensors, actuators and communication

- multiple bus adapters for parallel and serial busses

- special-purpose co-processors

- monitoring components to enhance reliability

Examples for such an architecture range from simple 8-bit CPU-based system to various PC-104 based embedded computers. The Cube System that is described in detail in section 3.1 is such an architecture.

One specific constraint for the hardware of an autonomous system it that it should perform its task as long as possible without direct human intervention. This type of autonomy can be achieved through various operating system functions, from unsupervised start (and restart) to automatic data logging and system diagnose. Moreover, the system has to recover from various failures automatically, including those of the operating system itself, or at least bring the system to a safe state. This usually involves specialized additional hardware such as watchdog devices (See 3.4.7).

#### 1.2.2 Programming language for system software implementation

To implement an operating system and application software for a microcomputer system, some amount of hardware-dependent startup code is necessary which has to be coded in assembler language.But almost all other software is written in a high level programming language.

For the operating system (and system software in general), the C programming language[KR88] is a good choice for the implementation, as it has been explicitly designed for system software implementation[Ker81]. However, some parts of an operating system apart from the startup code are highly machine dependent and are therefore also coded in assembler instructions. Most of the programming examples throughout this document and in the reference manual are written in C.

The C Programming Language has a long tradition in the implementation of operating systems, starting with UNIX in 1979[RT74, Tho78]. It has several constructs that facilitate direct hardware access, e.g. pointers and structures and has a clear relation between the high-level program and the machine instructions that are produced by the compiler, including a facility that allows mixed programs in C and assembler code.

By this, the C language forms a sound and extensible basis for the implementation of an operating system. But C also has its drawbacks, e.g. the lack of object orientation. However, as will be shown, this is not a limitation on the operating system level and user level programs can still be implemented in C++[Str91a, Str91b] since C and C++ code can easily coexist in the same program.

The C language has another advantage: Many other interpreted languages have a C-binding so that programs written in this language can call C-Functions. Moreover, their interpreters and virtual machines are often implemented in C or C++. By using C as implementation language, all these other languages (e.g. LISP, Java, PERL, Python) can be used for application programs by compiling their interpreters. But even compiler languages can easily be used in a C-based system by making use of converters such as f2c[F2C] (fortran to C) and p2c[Gil] (Pascal to C). However, the drawback of these converters is that they often produce inefficient code.

Throughout this document, the C language (ANSI C)[KR88] is used as a formalism for explaining algorithms. The code presented is mostly derived from the operating system code or application programs. Whenever the use of the C language would be to complex to illustrate a concept, a less formal pseudo-code language is used.

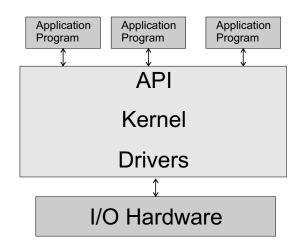

## 1.3 Operating system services for autonomous systems

To describe an operating system, one has to deal with a number of terms:

• According to [Tan87], the function of an operating system viewed from the application

programmers perspective is to define a set of "extended instructions" that are known as *system calls*.

- The set of system calls that an application program can use to communicate with the operating system is called an *Application Programming Interface*, short *API*.

- A *process* is a program in execution. Each process has an *address space* that is a list of memory locations the process can read and write. The address space contains program text (the instructions), program data (global variables, tables etc.) and (sometimes several) stack segments that are used to pass data to called functions and allocate local variables.

- A *thread* is one concurrently executing program function. A process can have multiple threads who share the address space of the process but have each their own stack segment. The execution within the program is switched from one thread to another either automatically (*preemptive multithreading*) or upon request (*cooperative multithreading*).

- a *CPU context* is the state of a CPU including status register, stack pointer and data and address registers. A CPU context can either be active, stored in a CPU or inactive, stored in memory.

Operating systems can be analyzed from a number of viewpoints. From the perspective of a end user of a computer system, the operating system is almost invisible. Therefore, the term operating system is often extended. One aspect of the extended uer view are system programs that deal with specific aspects of the operating system, such as the Unix Shell program or the Microsoft Windows Desktop. Another aspect are object code libraries. Although they are mostly hidden from the user's view, they implement common apects of user programs<sup>1</sup> and lead to a common "look and feel" of application programs.

As already stated in the introduction of this chapter, there are numerous requirements that an operating system for an autonomous system should support, several of which are contradictory. For example efficiency often contradicts configurability. Therefore, it is necessary to judge the requirements of the application to find an optimal trade-off.

For the use on autonomous systems, the operating system should support the following core services:

- concurrent thread execution

- inter-thread communication and synchronization

- interface code for sensor- and actuator devices

<sup>&</sup>lt;sup>1</sup>The common control library comctl32.dll in Microsoft Windows is one of the libraries that implement graphical dialogs e.g. for opening files.

- time measurement and realtime clock service

- communication service between multiple systems

- initialization services

Why these services are essential for the implementation of an autonomous system and how they are used will be shown in the following sections.

#### 1.3.1 Multithreading

A multithreading service consists of three parts. One is a data structure which contains the CPU state for each thread not currently running, together with some additional information about the thread. This data structure is commonly called *process table*. The next part is a routine which computes the next thread to be run. This routine is called *the scheduler*. The third part which is highly machine dependent is the *context switch*. This routine saves the current CPU state in one location of the process table and restores the state from another location of the process table and the other thread is stopped and its state is saved into the process table and the other thread for which the state has been restored from the process table can be executed.

There are multiple ways for the scheduler to decide which thread to execute next. The way in which the next thread is chosen can be based on global measures such as an equal distribution of CPU time over a number of threads or on local measures, i.e. which thread currently has the highest priority.

The simplest form of a scheduler is a round-robin scheduler. Whenever called, the scheduler switches immediately to the next thread in a circular list. Having run all threads once, the scheduler switches back to the first thread. By using some of the additional data in the process table, the behavior of the scheduler can be changed. One commonly used addition is a *suspend* flag. Whenever the flag is set, the thread will be skipped by the scheduler without running it. Setting the flag is usually called to *suspend* the thread, clearing the flag is called to *wake up* the thread. Another commonplace extension is a *thread priority*. Thread priority represents an ordering on the threads. Depending on the scheduler implementation, thread priority can have different semantics, e.g. lower priority threads are run less often than higher priority threads or the thread with the highest priority gets all the CPU time until it is suspended.

There are two principal ways to implement concurrent thread execution on a single CPU: *co-operative* and *preemptive* multi-threading. In cooperative multi-threading, the currently active thread has to explicitly give up the CPU by calling the scheduler, in preemptive multi-threading, the scheduler is called by a hardware function in fixed intervals. Both scheduling schemes have their advantages.

#### **Cooperative multi-threading**

Cooperative multi-threading's main advantage is that the thread can control in which state of its computation the scheduler is called. Consider for example a process doing data acquisition and communication.

Listing 1.1: data acquisition thread

```

#define BUFSIZE=1024

void data_acquisition_thread(){

int ad[4];

int i;

char DataBuffer[BUFSIZE];

while(1)

ł

/* gather some data... */

for (i=0;i<4;i++)

ad[i]=I2C_ReadAnalogIn(1,i);

/* Form a data packet */

sprintf(DataBuffer,"----DATA_PACKET----\n"

"AD1: %d\n"

"AD2:_%d\n"

"AD3:_%d\n"

"AD4:_%d\n",ad[0],ad[1],ad[2],ad[3]);

/* send the data packet away */

RSM send frame(DataBuffer);

/* call the scheduler */

KERN schedule();

}

}

```

By calling the scheduler after sending the data packet, is is ensured that a minimal time passes between the data acquisition and the data transmission since no other thread can interfere with the thread.

Depending on the number of other threads in the system, the actual rate of the readouts is undetermined. This rate may be important in several respects. First of all, the measurements may require it in order to be able to evaluate not only the actual value of the a/d conversion but also its changes over time, i.e. its first and second order derivatives. Another important reason for a predetermined readout rate is the communication bandwidth of the output channel. Reading more data than the output channel can transmit (in our case a simple frame-oriented communication network) will lead to increasing data queues and to data loss in case of nonblocking communication or to a undetermined temporal behavior of the readouts in case of blocking communication.

One solution to this problem could look like this:

Listing 1.2: fixed interval data acquisition

```

#define BUFSIZE=1024

#define READ_TIMEOUT=1000 /* milliseconds */

void data_acquisition_thread(){

int ad[4];

int i;

char DataBuffer[BUFSIZE];

int lasttime,lastticks;

int nowtime,nowticks;

lasttime=0;

lastticks=0;

while(1)

{

/* gather some data... */

read_clock(&lasttime,&lastticks);

for (i=0;i<4;i++)

ad[i]=I2C_ReadAnalogIn(1,i);

/* Form a data packet */

sprintf(DataBuffer,"----DATA_PACKET----\n"

"AD1:_%d\n"

"AD2:_%d\n"

"AD3: %d\n"

"AD4: %d\n",ad[0],ad[1],ad[2],ad[3]);

/* send the data packet away */

RSM_send_frame(DataBuffer);

/* call the scheduler until READ_TIMEOUT is over */

do {

KERN schedule();

read clock(&nowtime,&nowticks);

} while (

deltatime(nowtime, nowticks, lasttime, lastticks)

<READ_TIMEOUT);

}

}

```

This thread guarantees that no more than 1 packet is transmitted per second, by guaranteeing a minimal interval of 1000 milliseconds between two packets. It does not guarantee any maximal interval between two packets.

However, this program may still contain other calls to the scheduler that are not obvious since they can be hidden in some of the called API functions. For example, in the RoboCube, some A/D converters are connected to the CPU with the I<sup>2</sup>C serial bus system. Compared to the CPU bus, the I<sup>2</sup>C bus is slow. The internal I<sup>2</sup>C driver of CubeOS therefore uses a queuing scheme that allows multiple transfer requests to be queued. The I<sup>2</sup>C controller hardware processes these requests one by one and acknowledges this to the CPU. While the CPU waits for such a transaction to end, the thread starting the transaction must be stopped since it can only continue with the result from that transaction. While processing the A/D read request, the  $I^2C$  driver can simply waste CPU cycles by polling constantly if the request is already processed. Another alternative is to suspend the thread and run other threads in the meantime. Of course, the  $I^2C$  driver has to wakeup the thread as soon as the request is processed. As long as there is just one thread running, this does not change the way that the program is executed.

If a second thread is added that reads lots of data fast, e.g. from a digital camera, the situation changes. The code of such a thread might look like the function shown in the following listing:

Listing 1.3: image acquisition thread

```

#define IMAGESIZE=640*480

void image_processing_thread(){

int i;

char* ImageBuffer;

if !(ImageBuffer=malloc(IMAGESIZE))

return (-1);

init camera();

while(1)

{

/* read image from camera... */

while (!CamReady());

for (i=0;i<IMAGESIZE;i++)</pre>

ImageBuffer[i]=ReadCamByte();

}

ProcessImage(ImageBuffer);

KERN_schedule();

}

}

```

A quick analysis of this new thread shows the following properties:

- One run of the thread will probably take a long time, the size of the image data suggests this. However, the readout of one pixel is fast, so the thread will not give up the CPU for this.

- The thread is polling for the camera hardware to become ready. Without additional knowledge of the camera hardware, it cannot be determined how long this step might take.

- One part of the thread is completely hidden, it is unclear how long the ProcessImage() function takes to run, whether its runtime is constant or bound at all.

- Only after all three steps are executed, the thread calls the scheduler.

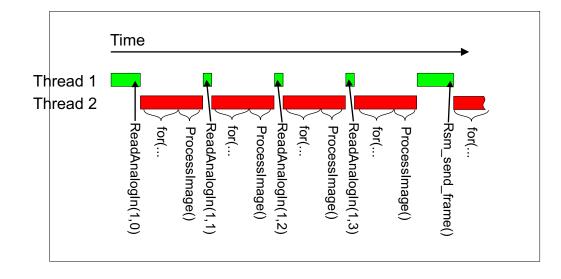

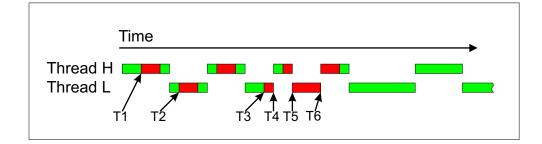

Figure 1.1 shows the execution flow for a system running these two threads. The image processing thread takes a long time for processing the image and the A/D readout thread can only work for a short while until it gives up the CPU again. This is probably not the way it was intended by the programmer of the first thread.

This problem could be "fixed" in several ways. One simple alternative would be to change the second thread in a way that it calls the scheduler more often.

Listing 1.4: "friendly" image acquisition

```

ProcessImage(ImageBuffer);

KERN_schedule();

}

```

However, the scheduler would waste a lot of CPU time being called that often. Moreover, the changes would have to be made inside the ProcessImage() function too.

A tradeoff would be to call the scheduler only after some instructions, e.g. after every 100 processed pixels. But that would not be sufficient in all cases, since the processing time for 100 pixels is not known and therefore, no timing could be assumed for the complete system.

#### Preemptive multi-threading

The clean solution to the problem is a preemptive scheduler. Unlike the cooperative scheduler, it is called by a timer interrupt, without any direct intervention of the thread. The runtime after which the current thread is interrupted and control is given to the scheduler is called the *time quantum*. The scheduler then decides if control is passed back to the current thread or to a different thread. (Note that direct intervention by calling the scheduler is still possible.)

The preemptive scheduler can interrupt the thread at every point in its execution flow (unless the thread takes explicit measures against it). Considering the last example, this resolves the problem of the long runtime of the second thread. However, the scheduler will also interrupt the first thread, lengthening the time between the readout of the A/D converter and the data transmission. One possibility to avoid this is to switch off the scheduler during this time.

Listing 1.5: preemptive data acquisition

```

#define BUFSIZE=1024

#define READ_TIMEOUT=1000 /* milliseconds */

void data_acquisition_thread(){

int ad[4];

int i;

char DataBuffer[BUFSIZE];

int lasttime,lastticks;

int nowtime,nowticks;

lasttime=0;

lastticks=0;

while(1)

{

disable_preemption();

/* gather some data... */

read_clock(&lasttime,&lastticks);

for (i=0;i<4;i++)

ad[i]=I2C_ReadAnalogIn(1,i);

/* Form a data packet */

```

```

sprintf(DataBuffer, "----DATA_PACKET----\n"

"AD1:_%d\n"

"AD2:_%d\n"

"AD3: %d\n"

"AD4: %d\n",ad[0],ad[1],ad[2],ad[3]);

/* send the data packet away */

RSM send frame(DataBuffer);

enable preemption();

/* call the scheduler until READ TIMEOUT is over */

do {

KERN schedule();

read clock(&nowtime,&nowticks);

} while (

deltatime(nowtime, nowticks, lasttime, lastticks)

<READ_TIMEOUT);

}

}

```

Once again, this is not an optimal solution since in this case, the scheduler is disabled during the readout of the A/D converter. As shown already, this can take some time. With the scheduler disabled, this time cannot be reused by another thread.

The alternative to this is to introduce priorities in the scheduler. By giving the data acquisition thread a higher priority than the image processing thread, it will always "win" over the image processing. Only while reading the A/D converter, the other thread will be run.

The next problem that arises is the implementation of the time delay. Since the data acquisition thread has a higher priority and remains unsuspended, calling the scheduler does not give up the CPU. The only solution for the thread here would be to lower its own priority while doing the time wait so that the other thread can be started. Lowering it below the priority of the other thread would lead to another problem since it would then be impossible to regain the CPU to increase the priority again after the timeout expires. If both threads would have the same priority, this would lead to the undesirable situation where only a part of the CPU time is available to the image processing thread while the rest is wasted on polling the timeout.

A clean solution to this is to enhance the scheduler with an additional function which disables a thread for a certain time.

```

Listing 1.6: scheduler-controlled KERN_sleep()

```

```

#define BUFSIZE=1024

#define READ_TIMEOUT=1000 /* milliseconds */

void data_acquisition_thread(){

int ad[4];

int i;

char DataBuffer[BUFSIZE];

int lasttime,lastticks;

int nowtime,nowticks;

```

```

lasttime=0;

lastticks=0;

while(1)

/* gather some data... */

for (i=0;i<4;i++)

ad[i]=I2C ReadAnalogIn(1,i);

/* Form a data packet */

sprintf(DataBuffer,"----DATA_PACKET----\n"

"AD1:_%d\n"

"AD2:_%d\n"

"AD3:_%d\n"

"AD4:_%d\n",ad[0],ad[1],ad[2],ad[3]);

/* send the data packet away */

RSM_send_frame(DataBuffer);

KERN_sleep_ms(READ_TIMEOUT);

}

}

```

In this case, the A/D thread keeps its higher priority but is still suspended by the explicit KERN\_sleep\_ms() call.

#### **1.3.2** Scheduling repetitive tasks

Repeated execution of *simple control tasks* (SCT) play an important role in most autonomous systems.

One typical example is motion control, which often makes use of some form of controller, e.g. PID-controllers[KD97]. Control theory assumes that these controllers are implemented continuously, i.e. with analog electronic components such as feedback amplifiers. However, today they are mostly implemented digitally as a repetitive task on a micro-controller.

Another example for these simple tasks can be the behaviors of reactive robotic architectures (see 1.1.3) and the layers of hierarchic robotic architectures (see 1.1.3).

What exactly is a SCT?

- A SCT has to be short in runtime. Usually, it has the structure of reading sensor values, executing some simple computations on these values and storing the result.

- A SCT does not block, i.e. it does not wait an unbounded period of time for external events. <sup>2</sup>

- When executed, a SCT runs to completion and exits.

<sup>&</sup>lt;sup>2</sup>For data acquisition, a SCT might wait, but this blocking usually is bounded to a very short time.

When multiple SCTs are present in a system, they often are executed in very different time intervals. One SCT monitoring ambient temperature may run once every few minutes where an SCT for motion control may run 1000 times a second.

Implementing SCTs within a system seems straightforward. For example, by making use of the preemptive scheduler, it is possible to schedule multiple SCTs in the following way. In this example, the SCTs are hidden within the SCT\_xxx() functions.

Listing 1.7: repetitive threads

```

void thread 1a(){

while(1)

{

SCT_do_something();

KERN_sleep_ms(1000);

ł

void thread_1b(){

while(1)

ł

SCT_do_something_too();

KERN_sleep_ms(1000);

}

void thread_2(){

while(1)

ł

SCT do something else();

KERN_sleep_ms(500);

}

void thread_3(){

while (1)

SCT_do_something_fast();

KERN_sleep_ms(250);

}

```

The preemptive scheduler would execute these threads in the following sequence, provided that there would be no interruption through preemption:<sup>3</sup>

<sup>&</sup>lt;sup>3</sup>Since the SCTs are short in runtime, it can be assumed that their execution is over before the time quantum for the current thread expires.

| Time    | $\rightarrow$ |     |    |    |

|---------|---------------|-----|----|----|

| 0 ms    | T1a           | T1b | T2 | T3 |

| 250 ms  | T3            |     |    |    |

| 500 ms  | T2            | T3  |    |    |

| 750 ms  | T3            |     |    |    |

| 1000 ms | T1a           | T1b | T2 | T3 |

And this scheme would be repeated over and over again.

With the given example, the repetitive execution of the tasks is not exactly as intended since the execution period is the sum of the execution time of the task and the wait time. To overcome this problem, two separate thread can be used to schedule each task, a control thread that does the scheduling and a worker thread that does the actual execution, as shown in the next example.

Listing 1.8: control thread and worker thread

```

void thread_1a_control(){

while(1)

{

KERN_wakeup(pid_of_worker_thread);

KERN_sleep_ms(10);

}

}

void thread_1a_worker(){

while(1)

{

KERN_suspend(getpid());

do_something();

}

}

```

As long as the CPU load is low, that means that the execution times are small compared to the wait times, this execution scheme is fine, but it can contain times where a high number of threads are to be executed where at other times, there are only few. For example, the previous example contains a high number of threads that are to be executed at 0 ms, and few at 250 and 750 ms.

However, if the delay times between two executions of a thread are the only specification, a scheme like the following would be more attractive:

| Time    | $\rightarrow$ |     |

|---------|---------------|-----|

| 0 ms    | T3            | T1a |

| 250 ms  | T3            | T2  |

| 500 ms  | T3            | T1b |

| 750 ms  | T3            | T2  |

| 1000 ms | T3            | T1a |

Here, the time delays are the same, but the threads are more evenly distributed. This means that this schedule can still be executed 'on time' even if the wait times are significantly lower. Moreover, implementing control and worker threads for every SCT is not very convenient and it also uses many resources of the system, e.g. the the process table of the preemptive scheduler. It is preferable to have an operating system service that handles SCTs and computes a schedule for their execution based on the specification of periods.

Parts of the following section have already been published in the SAB 2000 proceedings supplement book[BKS00], in the ICRA 2001 [BK01a] proceedings and in the SIRS 2000 [BK00] proceedings.

Here, a novel scheduling algorithm, the so-called B-scheduling<sup>4</sup>, is presented which handles SCTs running on different time-scales represented through so-called exponential effect priorities. Instead of directly specifying delay times in a linear way, an exponential scheme is used to specify them. Therefore, so-called *exponential effect priorities* are introduced here. The idea is that for each increase in a priority value by one, the execution frequency is halved.

In the remainder of this section the following naming conventions are used: the set of SCTs:  $S = \{s_0, ..., s_{N-1}\}$ , the priority-value of a SCT  $s_i$ :  $pv[s_i]$ , the set of SCTs with priority kor the k-th priority class:  $PC_k$ , and the highest used priority-value: maxpv. The definition of a priority-value  $pv[s_i]$  of SCT  $s_i$  within exponential effect priorities is that between two consecutive executions of any SCT  $u \in PC_{pv}$ , every SCTs in  $PC_{pv-1}$  is executed exactly twice.

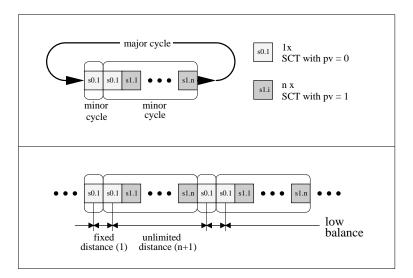

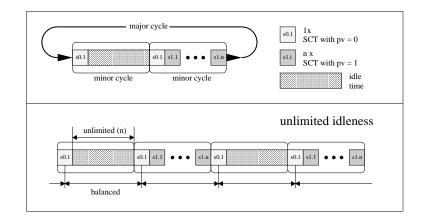

For solving the task of finding a suitable order of execution of the SCTs, a *cyclic executive scheduling* approach[BW97] is used. This means there is a so-called *major cycle*, which is constantly repeated. The major cycle consists of several *minor cycles*. Each minor cycle is a set of SCTs which are executed in a fixed order when the minor cycle is executed. Every SCT can be executed at most once per minor cycle, so the minor cycle can be a set. However, it is still assumed that the SCTs in a minor cycle are executed every time in a fixed sequence.

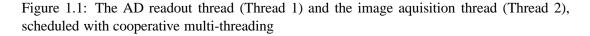

To illustrate the problems involved in scheduling, Figure 1.2 shows a simple algorithm, which schedules behaviors based on their priorities. The example shows the execution of one major cycle, the repetitive execution of the major cycles is omitted. The outer loop counts the minor cycles in *round*. The SCTs of priority-class  $PC_k$  are executed if *round* is a multiple of  $2^k$ . This scheduler produces a similar result as the repetitive scheduling which makes use of the preemptive scheduler in Listing 1.7.

This scheduler is correct since it produces a valid exponential effect schedule. The outer loop counts the minor cycles. The execution of the SCTs of a process class pv in round *i* is determined by the expression *i* modulo  $2^{pv}$  becoming zero. This expression actually truncates the most significant bits of *i* to zero so that only the bits  $b_{pv-1} \cdots b_0$  are passed on. For the process class pv - 1, the bits  $b_{pv-2} \cdots b_0$  are truncated. This means that by continuously incrementing *i*, for every time  $b_{pv-1} \cdots b_0$  becomes 0,  $b_{pv-2} \cdots b_0$  becomes 0 twice. The first time it

<sup>&</sup>lt;sup>4</sup>B stands for behavior since it has first been used in the context of scheduling behaviors in reactive robotics

/\* Execute the Major Cycle \*/ 1  $for(round = 0; round < n_{mic}; round = round + 1)$  { 2 3 /\* Execute the Minor Cycle \*/ 4 foreach  $s_{id} \in \mathcal{S}$ : {  $\operatorname{if}(round \operatorname{modulo}\ 2^{pv[s_i]} == 0) \ \{$ 5 6 execute  $s_{id}$ 7 } 8 } 9 }

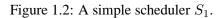

Figure 1.3: The simple scheduler  $S_1$  leads to a so-called unbalanced execution. One minor cycle can consist of a single SCT s0.1 while a second minor cycle contains unlimited many other SCTs. Hence, the execution of s0.1 is not evenly spread.

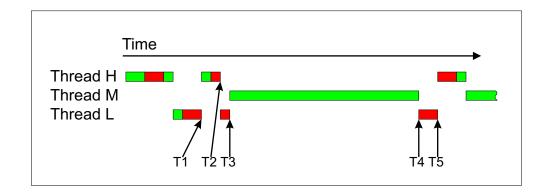

Figure 1.4: Adding idle time to balance the schedule made by  $S_1$  can lead to an unlimited waste of time.

becomes zero is when  $b_{pv-1} \cdots b_0$  is zero. The second time is when:

$$b_{pv-1}\cdots b_0 = 1\underbrace{0\cdots 0}_{pv-1\cdots 0}$$

The major problem with this algorithm is illustrated in Figure 1.3. Assume there is a SCT s0.1 with priority 0 and n SCTs s1.i with priority 1. So,  $\#PC_0 = 1$  and  $\#PC_1 = n$ . The first minor cycle consists of s0.1. As  $S_1$  executes all SCTs of a priority-class together, the second minor cycle includes all SCTs with priority 0 and priority 1, i.e., this minor cycle has n + 1 SCTs. From a naive viewpoint, it can be said that the SCTs are badly distributed.

In a more formal approach, the so-called *balance* of a schedule S is defined as

$$balance(S) = \min \frac{\min dist(s_i, x)}{\max dist(s_i, y)}$$

where x and y are minor cycles and  $dist(s_i, z)$  is the number of SCTs which are executed between start of the execution of  $s_i$  in cycle z and its next execution in cycle  $z + 2^{pv[s_i]}$ . If the balance is one, then the schedule manages an equidistant spreading of every SCT over the cycles. If the balances is close to zero than there is at least one SCT which is very unevenly executed.

A small balance is undesirable. As illustrated in the above example, a SCT with low priorityvalue, i.e., a SCT which should be executed very often, has to wait for an unbounded timeperiod. This is also expressed by the balance of  $S_1$  which is in this case:

$$balance(S_1) = \frac{1}{n} = 0 \text{ for } n \to \infty$$

The balance of  $S_1$  can be improved by adding idle time as illustrated in Figure 1.4. This way, the balance can always be tuned to reach the optimum of one. But this is bought at the cost of an unlimited waste of time. The *idleness* as the sum of idle-times in a major cycle is now unbounded.

In general, a schedule S is *time-optimal* if and only if the idleness is zero.

/\* Initialization \*/ 1 /\* computing the initial wait-values for each SCT  $s_{id}$  \*/ 2 3 quicksort( $\mathcal{P}$ ) 4 pc = 15 start = 06  $n_{slots} = 1$ 7 for(i = 0; i < maxpv; i + +) {  $start = 2 \cdot start$ 8 9  $n_{slots} = 2 \cdot n_{slots}$  $\forall id \text{ with } pv[s_{id}] = pc : \{$ 10 11  $wait[s_{id}] =$ reverse((start + id) modulo n<sub>slots</sub>) 12 } 13 start =14  $(start + \#\{s_{id} \mid pv[s_{id}] = pc\}) \mod n_{slots}$ 15 16 pc = pc + 117 }

Figure 1.5: The initialization of B-scheduling.

The workload WL within a major cycle can be computed as the sum of the occurrences of each SCT, i.e.

$$WL = \sum_{0 \le i \le maxpv} \#PC_i \cdot 2^{maxpv-i}$$

The number  $n_{mic}$  of minor cycles per major cycle is determined by the highest priority value maxpv as the SCT or the SCTs with this priority have to be executed once per major cycle. It follows that the average number av of SCTs per minor cycle has to be

$$av = WL / n_{mic}$$

with  $n_{mic} = 2^{maxpv}$

```

/* Execute the Major Cycle */

1

for(round = 0; round < n_{mic}; round = round + 1) {

2

/* Execute the Minor Cycle */

3

4

id = 0

5

done = 0

while (done < perfect) \land (id < \#P)) {

6

\texttt{if}(wait[s_{id}] == 0) \ \{

7

8

execute s_{id}

wait[s_{id}] = 2^{pv[s_{id}]}

9

done = done + 1

10

11

}

id = id + 1

12

13

}

\forall s_{id} \in \mathcal{P} : if(wait[s_{id}] > 0) : wait[s_{id}] = wait[s_i] -

14

1

15 }

```

Figure 1.6: The execution of a B-schedule.

Figure 1.7: Slots and Layers of a SCT schedule

For an even distribution of the workload, the actual number of SCTs in a minor cycle has to be equal to the average number av. Unfortunately, av is not necessarily an integer. Therefore, a distinction between

$$perfect = \lceil av \rceil$$

and  $dirty = \lfloor av \rfloor$

must be made.

A so-called *perfect minor cycle* has perfectly many SCTs, whereas the number of SCTs in a *dirty minor cycle* accordingly is *dirty*. A *bad minor cycle* includes more than *perfect* or less than *dirty* many SCTs.

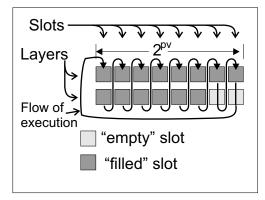

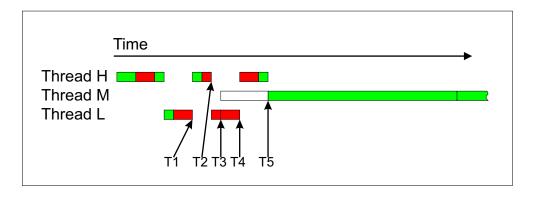

The sequence in which the SCTs are executed within the minor cycles defines a number of "Layers". A SCT in the *i*th layer of a minor cycle is executed as the *i*th SCT when that minor cycle is executed. This is shown in Figure 1.7.

B-scheduling computes a schedule  $S_B$  such that

- 1.  $S_B$  is time-optimal

- 2.  $S_B$  is a exponential effect schedule

- 3. A SCTs is in the same layer of all minor cycles in which it is executed.

- 4. the SCTs are distributed over the cycles so that  $s_i$  is executed in cycle  $c + 2^{pv[s_i]}$  if and only if  $s_i$  is executed in cycle c

- 5. the major cycle consists only of perfect and dirty minor cycles

It follows from properties 2,3 and 4 that S is well balanced as

$$balance(S_B) = \frac{dirty + 1}{perfect + 1}$$

(1.1)

$$= 1 \text{ for } av \to \infty \tag{1.2}$$

The worst-case balance of  $S_B$  is 1/2 when only two SCTs are used and one is more frequent than the other. In general, the balance becomes better the more workload is handled in each minor cycle.

What is the difference between this and the simple scheduler and why is this one so much better in terms of balance?

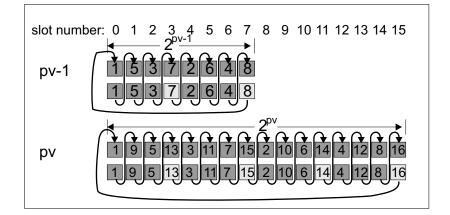

The simple scheduler executes all SCTs of a priority class pv in the minor cycle *i* where *i* modulo  $2^{pv}$  becomes zero. Then, in the following  $2^{pv} - 1$  minor cycles, no SCT of this class is executed. The B-Scheduler evenly distributes the elements of the priority class pv over the available  $2^{pv}$  minor cycles. For the priority class  $PC_0$ , this is easy since every element of  $PC_0$  is executed in every minor cycle. If there would be no SCTs in a higher priority class, the length of the major cycle would also be one.

In this case, there is exactly one possibility to add the SCT into a minor cycle. Therefore, the number of "slots", i.e. the number of possible minor cycles to add a SCT to is one, although the number of minor cycles in the final schedule might be higher. For the next priority class  $PC_1$  there are two slots, for priority class  $PC_i$  there are  $2^i$  slots. Figure 1.7 shows a schedule with eight slots of which six already contain two SCTs and two contain only one.

Whenever the number of processes in a priority class is a multiple of  $2^{pv}$ , the way in which the members are distributed over the  $2^{pv}$  available "slots" is irrelevant. This is the case since all minor cycles into which a SCT is "inserted" have the same number of SCTs after processing all SCTs of  $PC_{pv}$ . In detail, if the priority class pv has  $k2^{pv}$  members, these are distributed by the algorithm into k "layers" because each minor cycle gains k new SCTs.

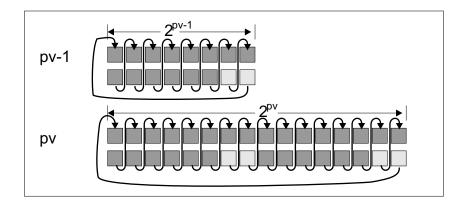

A problem arises if there is a remainder of empty slots after the insertion of priority class PCpv(which is assumed to be the lowest process class where there is such a reminder). This occurs if  $\#PC_{pv}$  modulo  $2^{pv} \neq 0$ , consequently, there are  $2^{pv} - (\#PC_{pv} \mod 2^{pv})$  empty "slots". To illustrate the connection with the perfect and dirty values defined before, if there would be no further SCTs to insert, there would be  $2^{pv} - (\#PC_{pv} \mod 2^{pv})$  dirty and  $\#PC_{pv}$ modulo  $2^{pv}$  perfect minor cycles. To be able to fill these empty slots in the dirty cycles by inserting processes of the next process class  $PC_{pv+1}$  before inserting a SCT into one of the perfect cycles (and thus forming a bad cycle), the location of the left-over dirty cycles (now called empty slots) must be known.

In terms of the original  $2^{pv}$  slots this is easy, the slots just have to be numbered. By maintaining a pointer to the next available empty slot, all empty slots can be found. If this pointer is to be used to identify the  $2^{pv+1}$  available slots in the next-higher process class, a problem arises. An operation has to be applied to the pointer to convert it from a pointer for process class pv to a pointer for process class pv + 1 so that:

- 1. for every empty slot in process class pv there are two empty slots in process class pv + 1

- 2. and the new value of the pointer identifies all empty process slots for process class pv+1 if its old value did identify all empty slots for the process class pv.

Obviously, this problem can be solved by maintaining a data structure that is used to remember all currently empty slots. When process class pv is processed, all empty slots that are still available from process class pv - 1 are replaced by two slots. If the original slot was in minor cycle *i* of process class pv - 1, then it is replaced by a slot in minor cycle *i* of process class pvand a slot in minor cycle  $i + 2^{pv-1}$ . This approach is illustrated in Figure 1.8.

Figure 1.8: Empty slots that are generated from the transition  $pv - 1 \rightarrow pv$

This problem can also be solved by the bit reverse function in line 12 of the program shown in Figure 1.5 without any additional datastructure.

The bit reverse function for a *n*-bit-value is defined as

$$bitreverse(n,v) = \sum_{i=0}^{n-1} 2^i bittest(v,n-i)$$

(1.3)

where bittest(v, i) tests if the  $2^i$  bit in v is set.

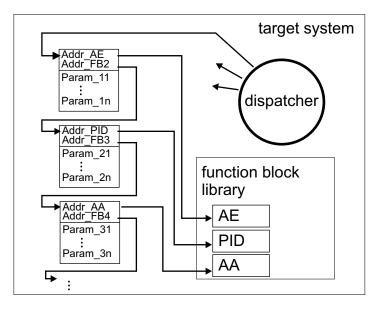

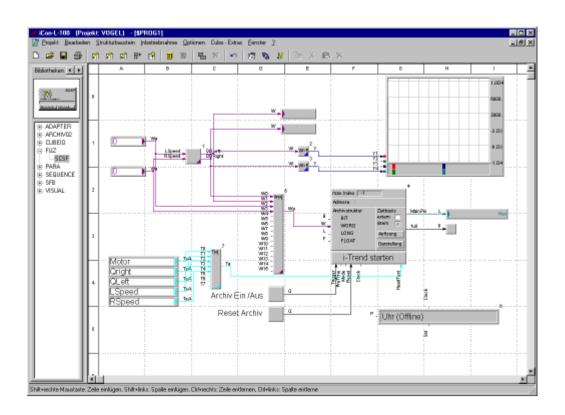

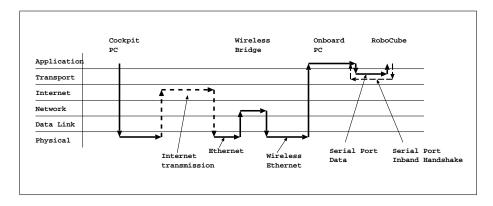

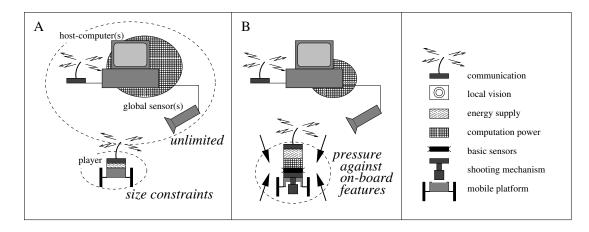

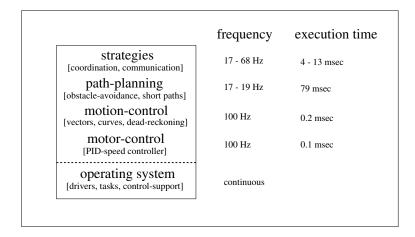

Or simpler, if  $v = b_n \cdots b_0$ , then  $bitreverse(n, v) = b_0 \cdots b_n$ .