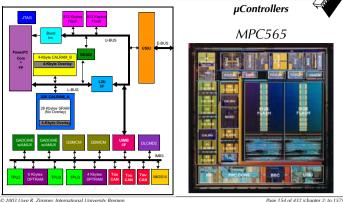

- Full scale integrated processor (MCP565)

- © 2003 Uwe R. Zimmer, International University Bremen

- Page 9 of 432 (chapter 0: to 12)

#### Table of contents

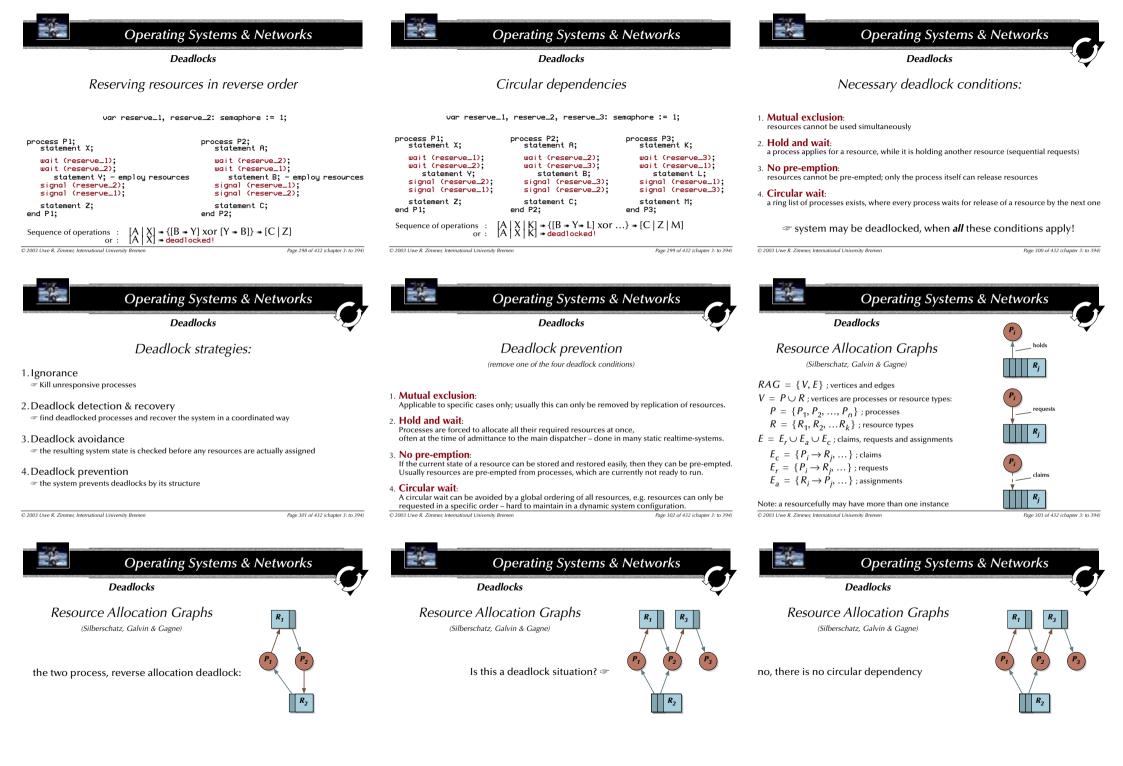

#### 3.2 Deadlocks

#### Ignorance & recovery

• # 'kill some seemingly persistently blocked processes from time to time' (exasperation)

#### Deadlock detection & recovery

- · @ multiple methods for detection, e.g. resource allocation graphs, Banker's algorithm

- recovery is mostly 'ugly'

#### Deadlock avoidance

• check system safety before allocating resources, e.g. Banker's algorithm

#### • Deadlock prevention

• *«* eliminate one of the pre-conditions for deadlocks

© 2003 Live R. Zimmer. International University Bremen

Page 10 of 432 (chapter 0: to 12)

Introduction

Uwe R. Zimmer – International University Bremen

# **Operating Systems & Networks**

**Operating Systems & Networks**

[Tanenbaum97]

[Tanenbaum95]

Prentice Hall, 1997

Prentice Hall, 1995

Andrew S. Tanenbaum

Distributed Operating Systems

References for this chapter

all references and some links are available on the course page

#### Table of contents

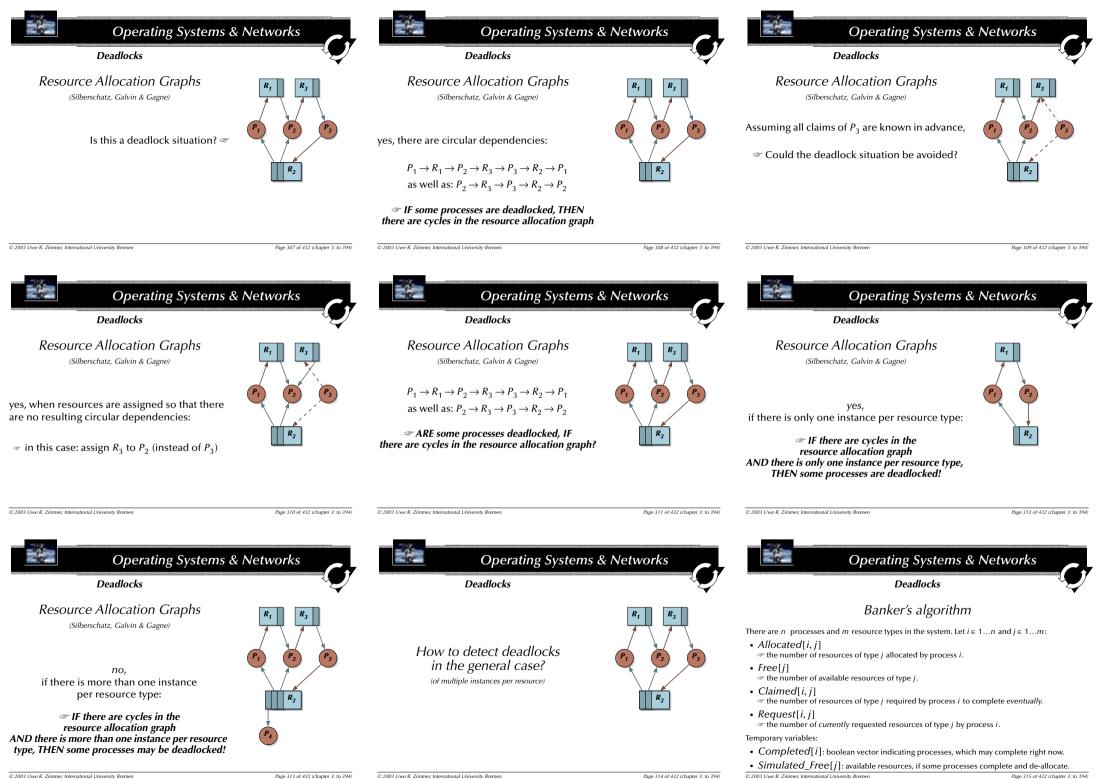

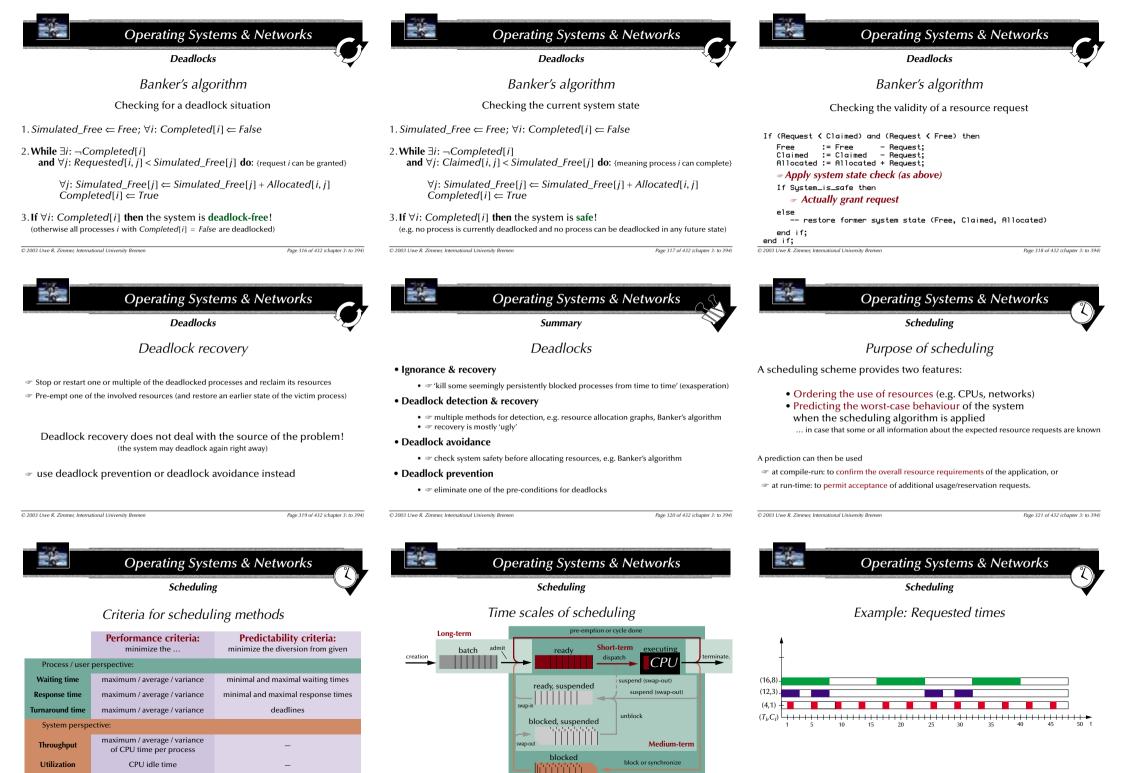

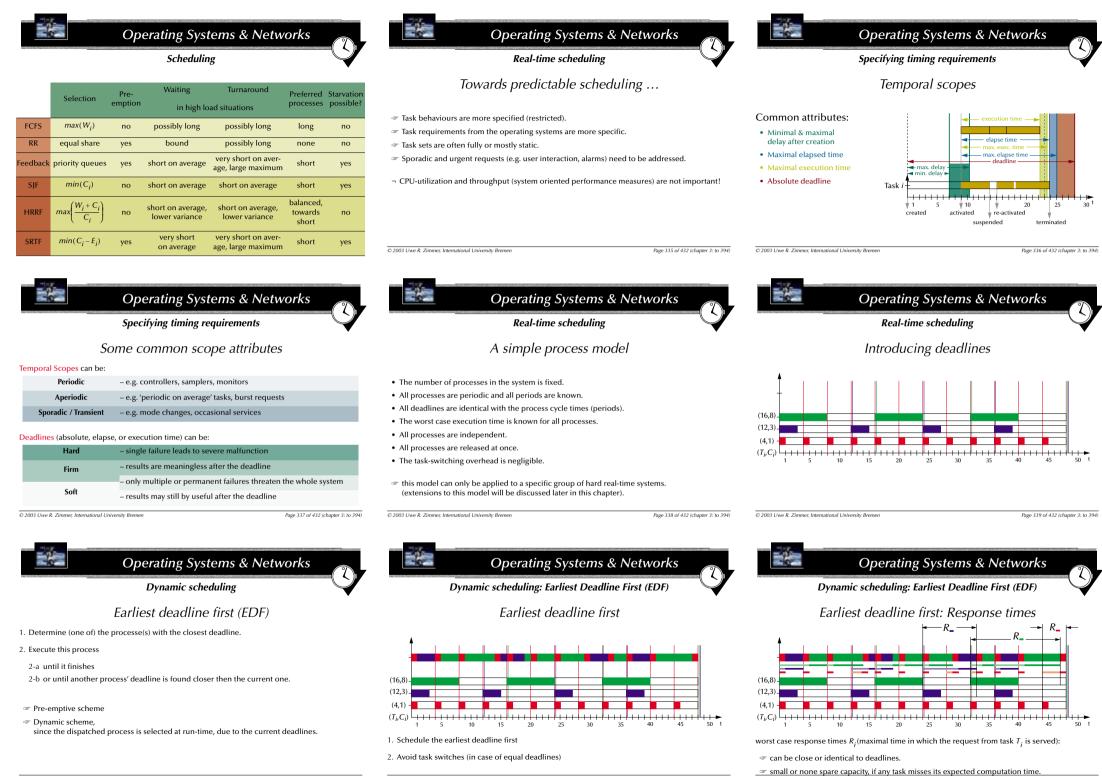

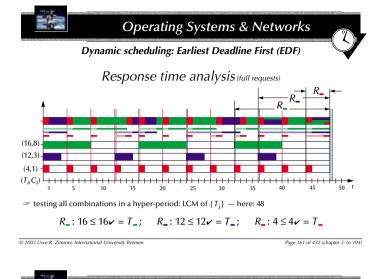

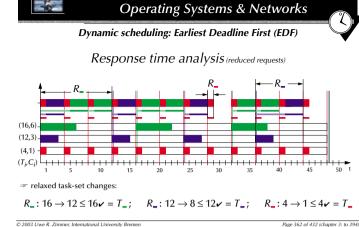

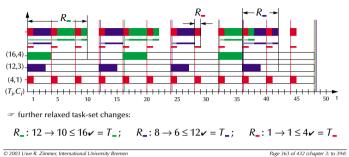

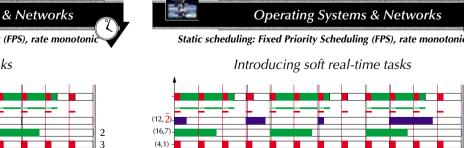

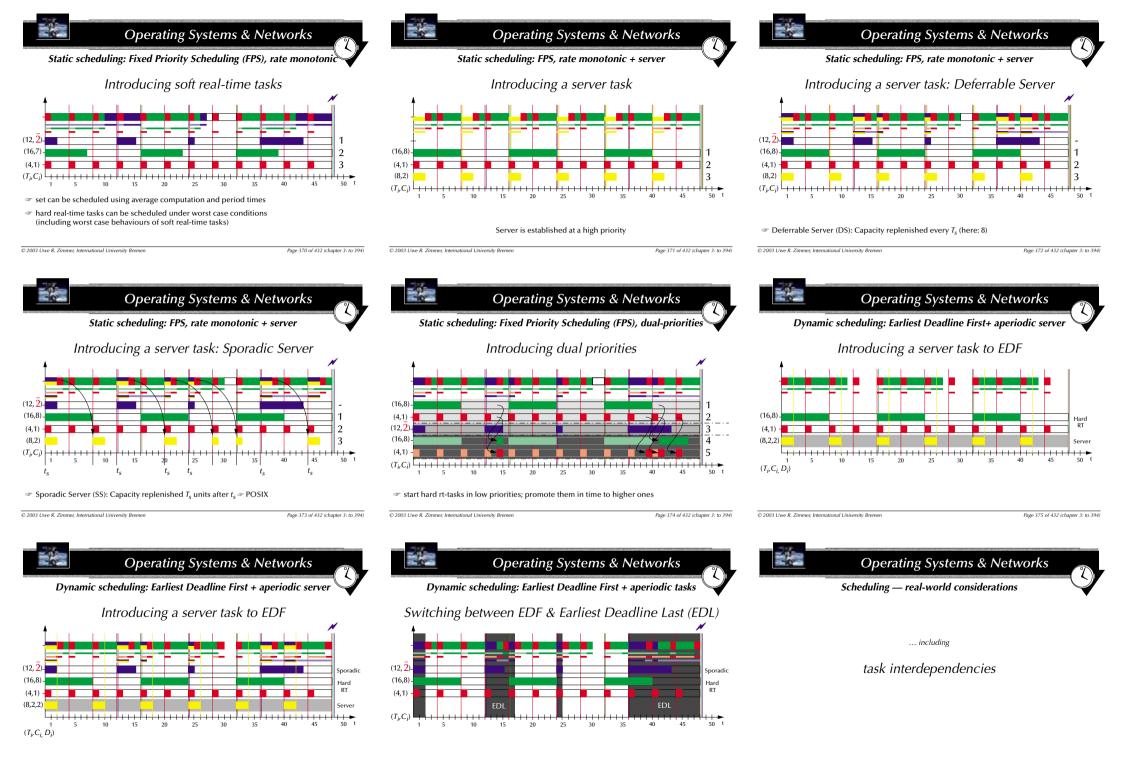

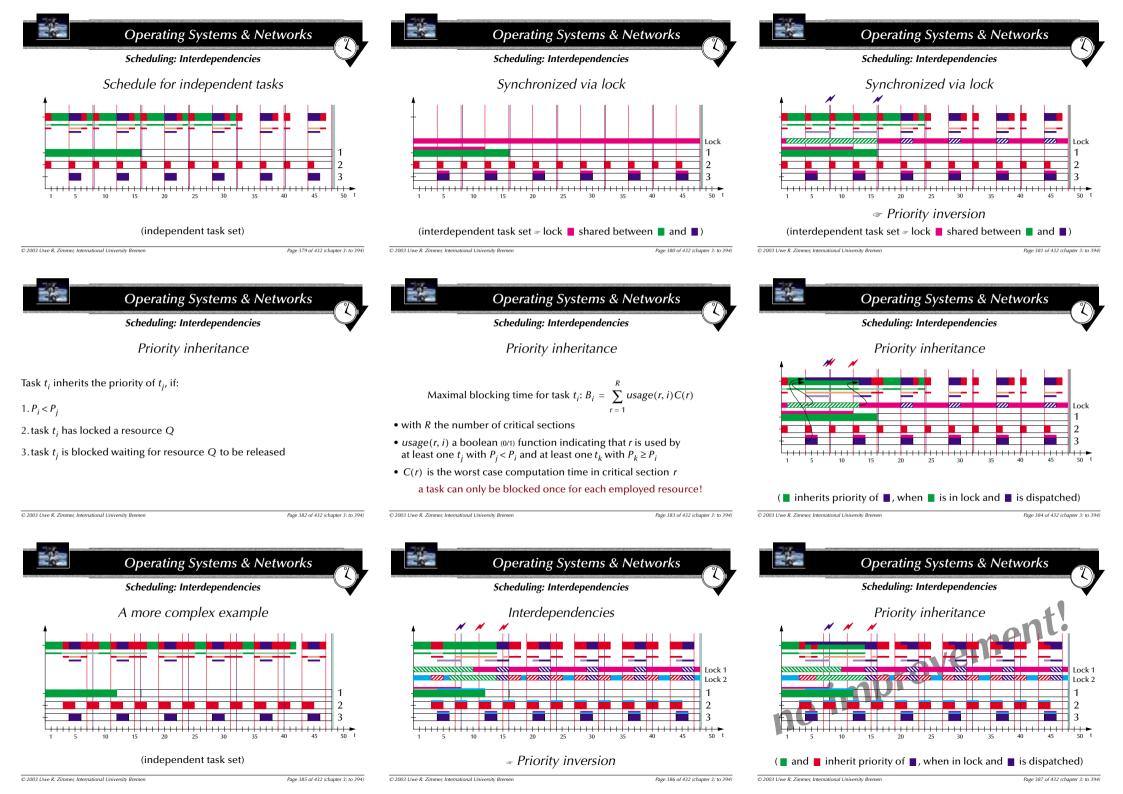

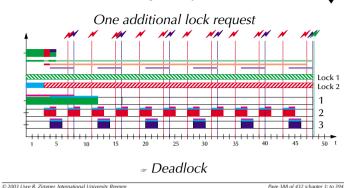

## 3.3 Scheduling

#### Basic performance based scheduling

- C: is not known: first-come-first-served (FCFS), round robin (RR),

- and feedback-scheduling C; is known: shortest job first (SJF), highest response ration first (HRRF) shortest remaining time first (SRTF)-scheduling

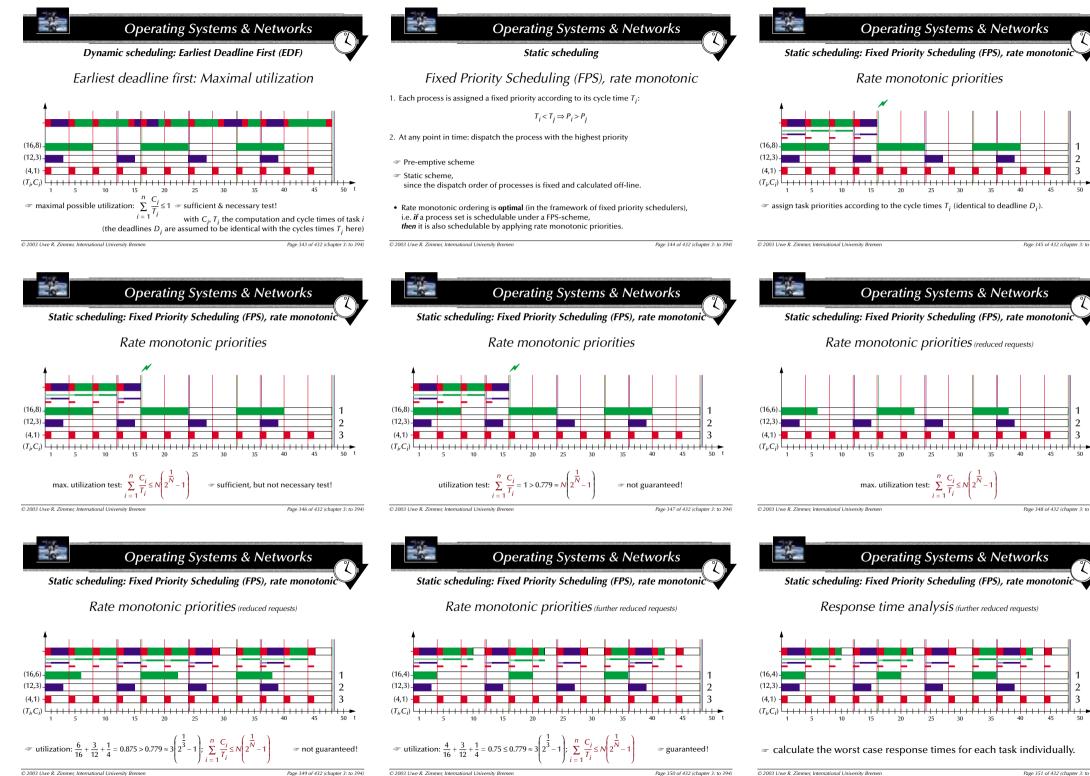

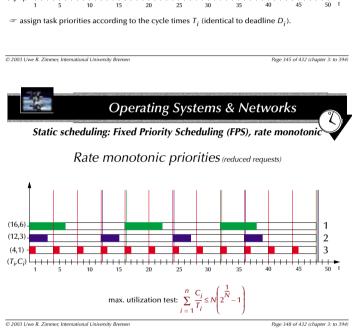

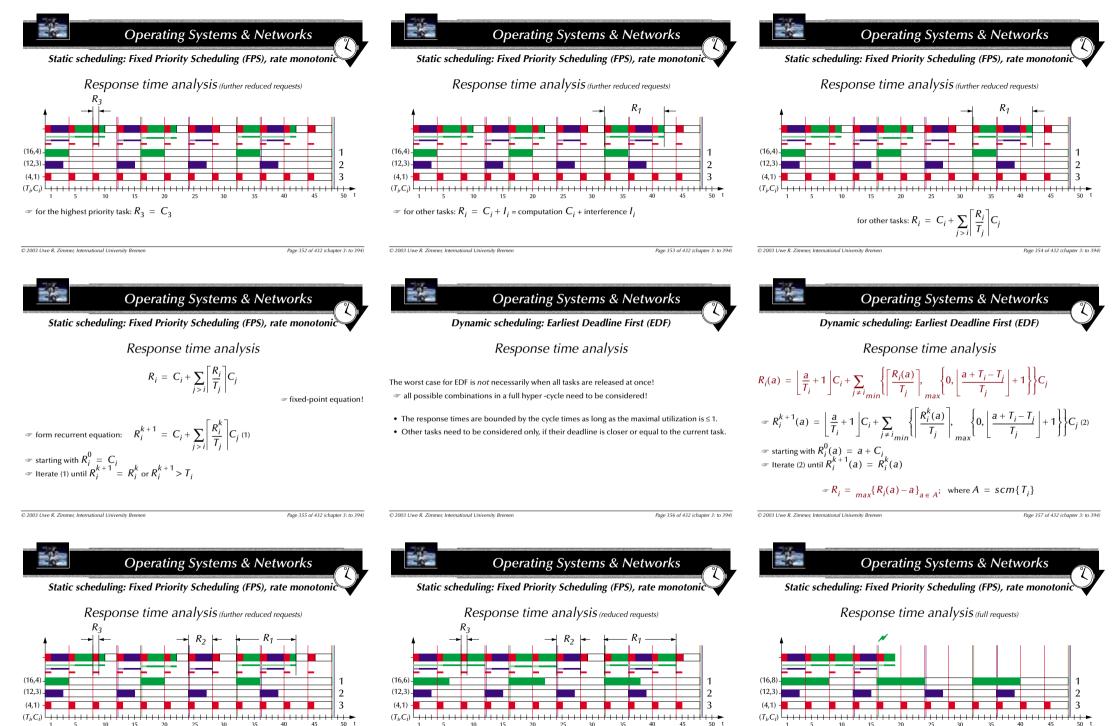

#### Basic predictable scheduling

• Fixed Priority Scheduling (FPS) with Rate Monotonic (RMPO) Earliest Deadline First (EDF)

#### Real-world extensions

[Silberschatz01]

[Stallings2001]

Greg Gagne

William Stallings

Operating Systems

Prentice Hall, 2001

Operating System Concepts

John Wiley & Sons, Inc., 2001

· Aperiodic, sporadic, soft real-time tasks

Abraham Silberschatz, Peter Bear Galvin,

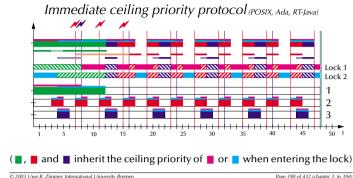

• Synchronized talks (priority inheritance, priority ceiling protocols)

© 2003 Live R. Zimmer. International University Bremen

Page 11 of 432 (chapter 0: to 12)

Andrew S. Tanenbaum, Albert S. Woodhull

Operating Systems: Design and Implementation

# **Operating Systems & Networks**

**Operating Systems & Networks**

Table of contents

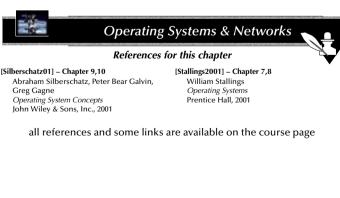

4. Memorv

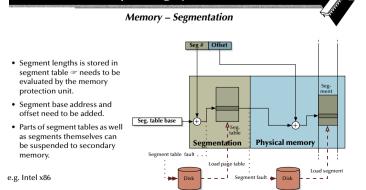

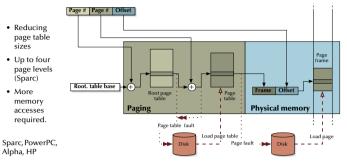

Simple paging, multi-level paging, combined segmentation & paging

#### What are operating system based on?

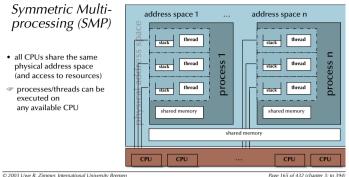

#### Hardware environments / configurations:

- stand-alone, universal, single-processor machines

- · symmetrical multiprocessor-machines

- · local distributed systems

- · open, web-based systems

- · dedicated/embedded computing

© 2003 Live R. Zimmer, International Liniversity Bremer

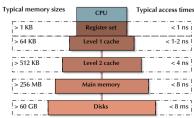

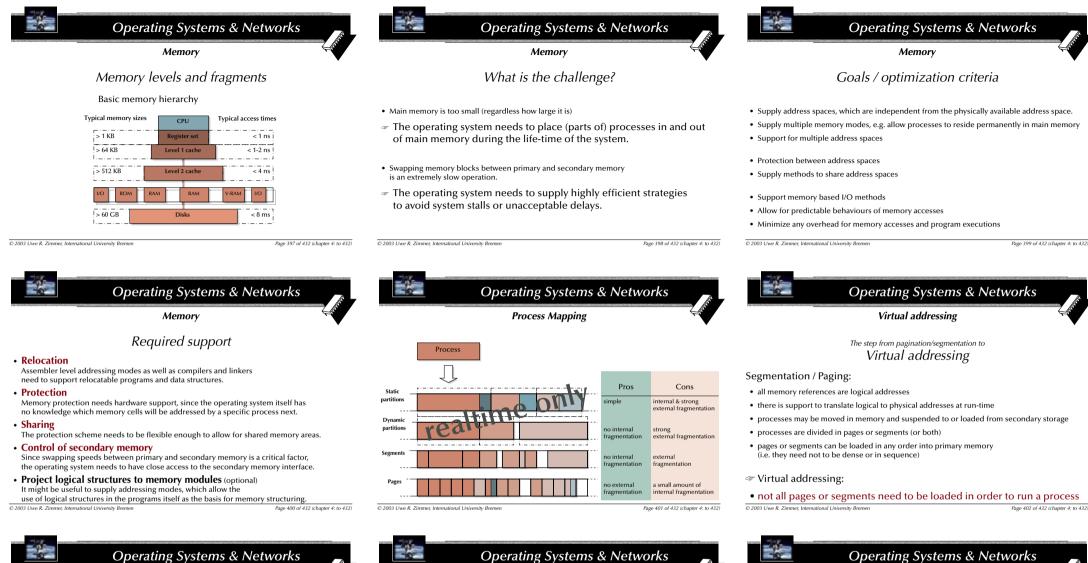

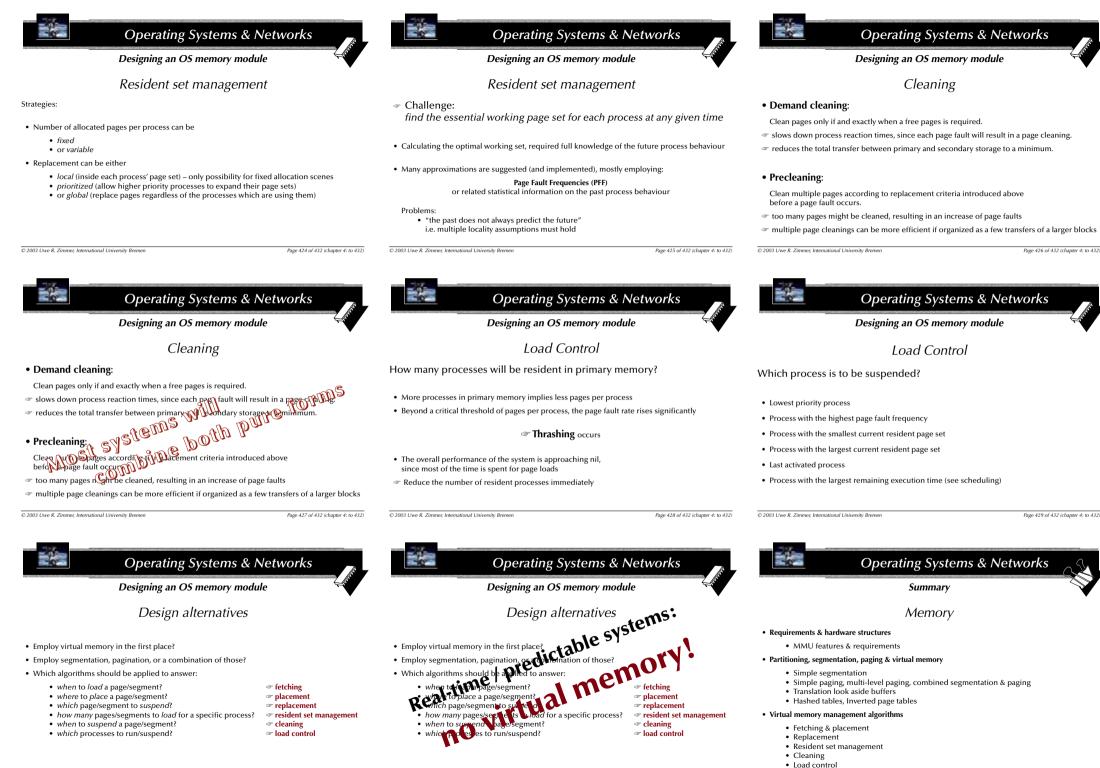

· Requirements & hardware structures

• Simple segmentation

Virtual memory management algorithms

Fetching & placement

Replacement · Resident set management

Load control

© 2003 Liwe R. Zimmer. International University Bremen

Cleaning

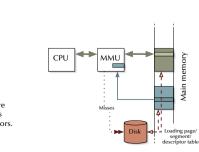

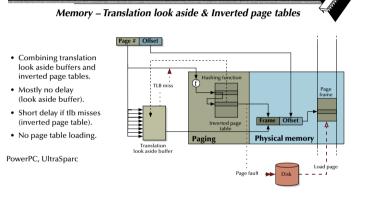

MMU features & requirements

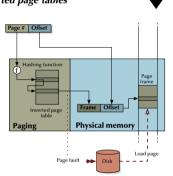

· Translation look aside buffers

· Partitioning, segmentation, paging & virtual memory

Hashed tables, Inverted page tables

## What is the common ground for operating systems?

## What is an operating system?

## **Operating Systems & Networks**

#### What is an operating system?

1. A virtual machine!

... offering a more comfortable, robust, reliable, flexible ... machine

| Tasks           |                       |                      |

|-----------------|-----------------------|----------------------|

| OS              | Tasks                 | Tasks                |

| Hardware        | RT-OS<br>Hardware     | Hardware             |

| Typ. general OS | Typ. real-time system | Typ. embedded system |

© 2003 Uwe R. Zimmer. International University Bremer

# **Operating Systems & Networks**

#### What is an operating system?

2. A resource manager!

... dealing with all sorts of devices and coordinating access

Operating systems deal with

- · processors,

- memory

- mass storage

- · communication channels

- devices (timers, special purpose processors, interfaces, ...)

- and many tasks/processes/programs, which are applying for access to these resources

**Operating Systems & Networks** What is an operating system? Is there a standard set of features for an operating system? the term 'operating systems' covers 4KB kernels, as well as 1GB installations of general purpose OSs. Is there a minimal set of features?

#### ☞ almost

memory management, process management and inter-process communication/synchronization will be considered essential in most systems.

## Is there always an explicit operating system?

some languages and development systems operate with stand-alone run-time-environments. Page 18 of 432 (chapter 1: to 89) © 2003 Uwe R. Zimmer. International University Bremen

© 2003 Uwe R. Zimmer, International University Bremen

Page 17 of 432 (chapter 1: to 89)

Page 14 of 432 (chapter 1: to 89)

Page 12 of 432 (chapter 0: to 12)

Page 15 of 432 (chapter 1: to 89)

#### The evolution of operating systems

- in the beginning: single user, single program, single task, serial processing an OS

- 50s: System monitors / batch processing

- The monitor ordered the sequence of jobs and triggered their sequential execution

- 50s-60s: Advanced system monitors / batch processing: or the monitor is handling interrupts and timers

- first support for memory protection

- ar first implementations of privileged instructions (accessible by the monitor only).

- early 60s: Multiprogramming systems: ar employ the long device I/O delays for switches to other, runable programs

- early 60s: Multiprogramming, time-sharing systems: assign time-slices to each program and switch regularly

- early 70s: Multitasking systems multiple developments resulting in UNIX (besides others)

- · early 80s: single user, single tasking systems, with emphasis on user interface (MacOS) or APIs. MS-DOS, CP/M, MacOS and others first employed 'small scale' CPUs (personal computers).

- mid-80s: Distributed/multiprocessor operating systems modern UNIX systems (SYSV, BSD)

© 2003 Live R. Zimmer. International University Bremen

Page 19 of 432 (chapter 1: to 89)

Infrared communication (e.g. IrDA) Modem

© 2003 L/we R. Zimmer. International University Bremen

# **Operating Systems & Networks**

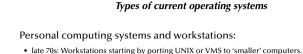

#### Types of current operating systems

#### Parallel operating systems

• support for a large number of processors, either:

- symmetrical each CPU has a full copy of the operating system

- asymmetrical:

or

- only one CPU carries the full operating system,

- the others are operated by small operating system stubs to transfer code or tasks.

#### **Operating Systems & Networks**

#### The evolution of communication systems

- 1901: first wireless data transmission (Morse-code from ships to shore)

- · '56: first transmission of data through phone-lines

- · '62: first transmission of data via satellites (Telstar)

- '69: ARPA-net (predecessor of the current internet)

- 80s: introduction of fast local networks (LANs): ethernet, token-ring

- 90s: mass introduction of wireless networks (LAN and WAN)

#### Currently: standard consumer computers come with

- · High speed network connectors (e.g. GB-ethernet)

- Wireless LAN (e.g. IEEE802.11)

- Local device bus-system (e.g. firewire)

- Wireless local device network (e.g. bluetooth)

# **Operating Systems & Networks**

#### Types of current operating systems

#### Distributed operating systems

- all CPUs carry a small kernel operating system for communication services.

- · all other OS-services are distributed over available CPUs

- · services may migrate

- · services can be multiplied in order to

- guarantee availability (hot stand-by)

- · or to increase throughput (heavy duty servers)

- 80s: PCs starting with almost none of the classical OS-features and services. but with an user-interface (MacOS) and simple device drivers (MS-DOS)

- Iast 20 years: evolving and expanding into current general purpose OSs:

- Solaris (based on SVR4, BSD, and SunOS)

- LINUX (open source UNIX re-implementation for x86 processors and others)

- · current Windows (proprietary, partly based on Windows NT, which is 'related' to VMS)

**Operating Systems & Networks**

- MacOS X (Mach kernel with BSD Unix and an proprietary user-interface)

- · Multiprocessing is supported by all these OSs to some extend.

- None of these OSs is very suitable for embedded systems, also trials have been performed.

- All of these OSs are not suitable at all for distributed or real-time systems.

Page 21 of 432 (chapter 1: to 89)

# **Operating Systems & Networks**

Types of current operating systems

#### Real-time operating systems

© 2003 Live R. Zimmer. International University Bremen

1

- Fast context switches? should be fast anyway

- Small size?

should be small anyway

- Quick responds to external interrupts? or not 'quick', but predictable

- Multitasking? or real time systems are often multitasking systems

- 'low level' programming interfaces? or needed in many operating systems

- Interprocess communication tools? or needed in almost all operating systems

- High processor utilization? or fault tolerance builds on redundancy!

© 2003 Live R. Zimmer, International Liniversity Bremen

Page 22 of 432 (chapter 1: to 89)

© 2003 Uwe R. Zimmer. International University Bremer

Page 23 of 432 (chapter 1: to 89)

Page 20 of 432 (chapter 1: to 89)

© 2003 Live R. Zimmer, International University Bremen

© 2003 Uwe R. Zimmer, International University Bremer

Page 24 of 432 (chapter 1: to 89

# **Operating Systems & Networks**

#### Types of current operating systems

Real-time operating systems requesting ...

- The logical correctness of the results as well as

- the correctness of the time, when the results are delivered

Predictability! (not performance!)

All results are to be delivered just-in-time – not too early, not too late.

Timing constraints are specified in many different ways ... ... often as a response to 'external' events @ reactive systems

© 2003 Uwe R. Zimmer. International University Bremen

# **Operating Systems & Networks**

#### Roots of current commercial operating systems

**Operating Systems & Networks**

#### Types of current operating systems

#### Embedded operating systems

very small footprint (often a few KBs)

· none or limited user-interaction 90-95% of all processors are working here!

· usually real-time systems, often hard real-time systems

(hierarchical) Finite state machines synchronous languages: Esterel, syncEifel, synERJY, ...

## Programming styles alternatives

Imperative  $\leftrightarrow$  Functional  $\leftrightarrow$  Declarative  $\leftrightarrow$  Data-flow  $\leftrightarrow$  Finite state machines Static ↔ Dynamic Modular ↔ Concurrent ↔ Distributed Synchronous ↔ Continuous time Control oriented ↔ Data oriented

- Concurrency

support for tasking/threading

- Distribution

support for message passing or rpc

- Reliability @ detect errors at compile-time or in the run-time environment

- Large systems @ scalable, modular, or object-oriented + separate compilation

- Predictability

Page 34 of 432 (chapter 1: to 89)

operations which will lead to unforeseeable timing behaviours (e.g. garbage collection)

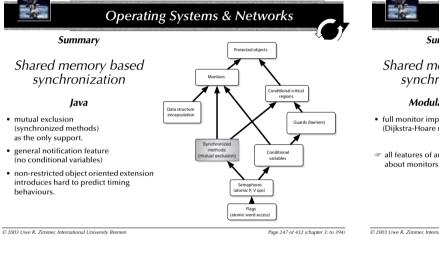

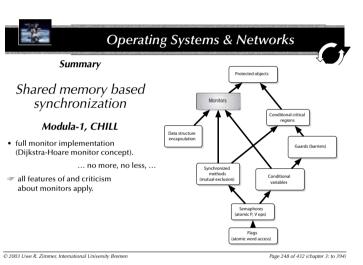

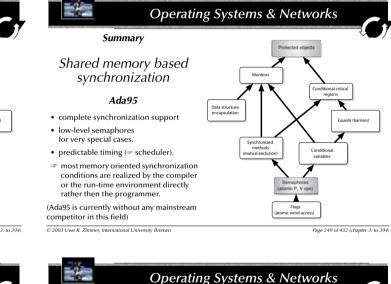

- Ada95 (for your understanding)

- JAVA (for some distribution and object orientated features)

- POSIX (as the IEEE standard for (UNIX-) OS interfaces)

- ... others in places

#### Ada95

Ada95 is a standardized (ISO/IEC 8652:1995(E)) 'general purpose' language with core language primitives for

- strong typing, separate compilation (specification and implementation), object-orientation,

- concurrency, monitors, rpcs, timeouts, scheduling, priority ceiling locks

- strong run-time environments

- ... and standardized language-annexes for

- additional real-time features, distributed programming, safety and security issues.

```

© 2003 Live R. Zimmer. International University Bremen

```

- system-level programming, numeric, informations systems,

- ... refreshing:

- specification and implementation (body) parts, basic types

- exceptions

- information hiding in specifications ('private')

- generic programming

- class-wide programming ('tagged types')

- monitors and synchronisation ('protected', 'entries', 'selects', 'accepts')

A simple queue implementation

procedure Engueue (Item: in Element: Queue: in out Queue\_Tupe) is

**Operating Systems & Networks**

Ada95

A crash course

abstract types and dispatching

package body Queue\_Pack\_Simple is

© 2003 Liwe R. Zimmer. International University Bremen © 2003 Uwe R. Zimmer. International University Bremen Page 38 of 432 (chapter 1: to 89)

**Operating Systems & Networks**

... introducing:

constants

The second

beain

some type attributes

parameter specification

Page 39 of 432 (chapter 1: to 89)

**Operating Systems & Networks**

#### A simple queue specification

package Queue\_Pack\_Simple is

OueueSize : constant Positive := 10: type Element is new Positive range 1\_000..40\_000; tupe Marker is mod OueueSize: type List is array (Marker'Range) of Element; type Queue\_Type is record Top, Free : Marker := Marker'First; Elements : List; end record: procedure Engueue (Item: in Element; Queue: in out Queue\_Type);

procedure Dequeue (Item: out Element; Queue: in out Queue\_Type);

end Queue\_Pack\_Simple;

© 2003 Live R. Zimmer. International Liniversity Bremen

Page 40 of 432 (chapter 1: to 89)

Page 43 of 432 (chapter 1: to 89)

Page 37 of 432 (chapter 1: to 89)

© 2003 Live & Zimmer International Liniversity Bremer

Page 41 of 432 (chapter 1: to 89)

© 2003 Live R. Zimmer, International University Bremen

procedure Queue\_Test\_Simple is

Queue : Queue\_Type;

Enqueue (2000, Queue);

Dequeue (Item, Queue);

Item : Element:

end Queue\_Test\_Simple;

Page 42 of 432 (chapter 1: to 89

# **Operating Systems & Networks** Ada95 Exceptions ... introducing: exception handling • enumeration types functional type attributes

**Operating Systems & Networks**

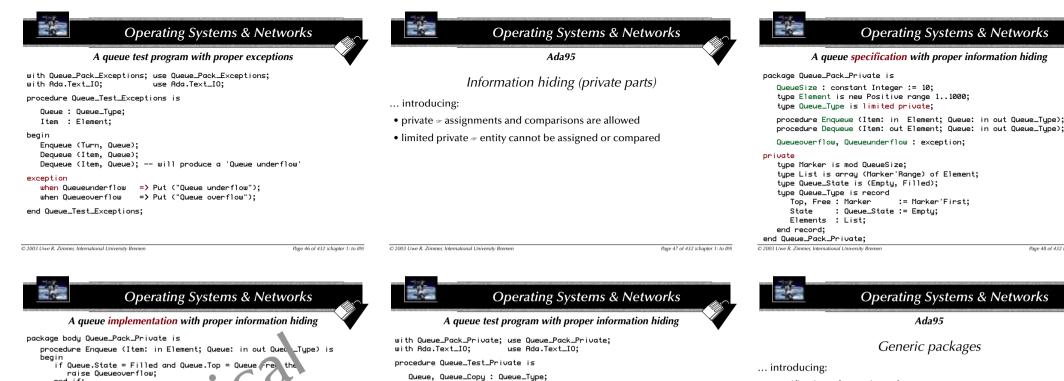

#### A queue specification with proper exceptions

package Queue\_Pack\_Exceptions is

OueueSize : constant Integer := 10: type Element is (Up, Down, Spin, Turn); type Marker is mod QueueSize; type List is array (Marker'Range) of Element; type Queue\_State is (Empty, Filled); type Queue\_Type is record Top, Free : Marker := Marker'First:

State : Queue\_State := Empty; Elements : List; end record:

procedure Enqueue (Item: in Element; Queue: in out Queue\_Type); procedure Dequeue (Item: out Element; Queue: in out Queue\_Type);

Queueoverflow, Queueunderflow : exception;

end Queue\_Pack\_Exceptions;

© 2003 Uwe R. Zimmer. International University Bremen

© 2003 Uwe R. Zimmer. International University Bremen Page 44 of 432 (chapter 1: to 89)

# **Operating Systems & Networks**

**Operating Systems & Networks**

**Operating Systems & Networks**

A simple queue test program

Dequeue (Item, Queue); -- will produce an unpredictable result!

Ada95

Basics

• specification and implementation (body) parts

with Queue\_Pack\_Simple; use Queue\_Pack\_Simple;

some basic types (integer specifics)

#### A queue implementations with proper exceptions

package body Queue\_Pack\_Exceptions is procedure Engueue (Item: in Element; Queue: in out Queue\_Type) is begin if Queue.State = Filled and Queue.Top = Queue.Free then raise Queueoverflow; end if; Queue.Élements (Queue.Free) := Item; Queue.Free := Marker'Pred (Queue.Free); Queue.State := Filled; end Enqueue; procedure Dequeue (Item: out Element; Queue: in out Queue\_Type) is begin if Queue.State = Empty then raise Queueunderflow; end if; Item := Queue.Elements (Queue.Top); Queue.Top := Marker'Pred (Queue.Top); if Queue.Top = Queue.Free then Queue.State := Empty; end if; end Dequeue; end Queue\_Pack\_Exceptions;

end Dequeue:

end Queue\_Pack\_Simple;

end Enqueue; procedure Dequeue (Item: out Element; Queue: in out Queue\_Type) is beain

begin

:= Queue.Elements (Queue.Top); Item

Oueue.Free := Oueue.Free - 1:

Queue.Top := Queue.Top - 1;

Queue.Elements (Queue.Free) := Item;

Item

exception

Page 49 of 432 (chapter 1: to 89)

Queue\_Copy := Queue;

when Queueoverflow

© 2003 Live R. Zimmer. International Liniversity Bremer

end Oueue\_Test\_Private:

Dequeue (Item, Queue);

beain

: Element;

Dequeue (Item, Queue); -- will produce a 'Queue underflow

when Queueunderflow => Put ("Queue underflow");

Enqueue (Item => 1, Queue => Queue);

```

raise Queueoverflow:

end if:

Queue.Élements (Queue.Free) := Item;

Queue.Free := Queue.Free - 1;

Oueue.State := Filled:

end Enqueue;

procedure Dequeue (Item: out Teme t; Queue: in out Queue_Type) is

begin

if Queue.State = Eloty then

raise Quelles der low;

end if;

Item : Queu. Elements

Queue.To, := Ducue.Top - 1;

: Quev. Elements (Queue.Top);

if Queue. p = Queue.Free then Queue.State := Empty; end if;

end Dequeue:

end Oueue_Pack_Private:

© 2003 Live R. Zimmer. International Liniversity Bremen

```

| 44.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operating Systems & Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| A generic queue implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| package body Queue_Pack_Generic is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| <pre>procedure Enqueue (Item: in Element; Queue: in out Queu_Type) is<br/>begin<br/>if Queue.State = Filled and Queue.Top = Queue rre; the<br/>raise Queueoverflow;<br/>end if;<br/>Queue.Elements (Queue.Free) := Item;<br/>Queue.Free := Queue.Free - 1;<br/>Queue.State := Filled;<br/>end Enqueue;<br/>procedure Dequeue (Item: out Tlement; Queue: in out Queue_Type) is<br/>begin<br/>if Queue.State = E big then<br/>raise Queres der low;<br/>end if,<br/>Item : Queue Elements (Queue.Top);<br/>Queue.Top := Queue.Free then Queue.State := Empty; end if;<br/>end Dequeue;</pre> |

| end Queue_Pack_Generic;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

-- compiler-error: left hand of assignment must not be limited type

=> Put ("Oueue overflow");

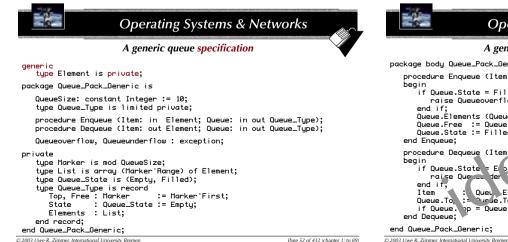

Generic packages ... introducing: specification of generic packages instantiation of generic packages

Top, Free : Marker

Elements : List;

© 2003 Live R. Zimmer, International Liniversity Bremer

State : Queue\_State := Empty;

**Operating Systems & Networks**

A queue specification with proper information hiding

:= Marker'First;

Ada95

**Operating Systems & Networks**

Page 48 of 432 (chapter 1: to 89)

Page 51 of 432 (chapter 1: to 89

Page 50 of 432 (chapter 1: to 89)

Page 53 of 432 (chapter 1: to 89)

```

Operating Systems & Networks

A generic queue test program

with Queue_Pack_Generic;

with Ada.Te×t_IO;

use Ada.Text_IO;

procedure Queue_Test_Generic is

package Queue_Pack_Positive is

new Queue_Pack_Generic (Element => Positive);

use Queue_Pack_Positive;

Queue : Queue_Type;

Item : Positive:

begin

Engueue (Item => 1, Oueue => Oueue):

Dequeue (Item, Queue);

Dequeue (Item, Queue); -- will produce a 'Queue underflow'

exception

when Oueueunderflow => Put ("Queue underflow");

when Oueueoverflow => Put ("Oueue overflow");

end Queue_Test_Generic;

© 2003 Uwe R. Zimmer. International University Bremen

Page 54 of 432 (chapter 1: to 89)

```

procedure Enqueue (Item: in Element; Queue: in out Ext\_Queue\_Type); procedure Read\_Queue (Item: out Element; Queue: in out Ext\_Queue\_Type);

end Oueue\_Pack\_Object:

| rnational University Bremen | Page 58 of 432 (chapter 1: to 89) |

|-----------------------------|-----------------------------------|

|                             |                                   |

| <b>Operating Systems</b>    | & Networks                        |

| Ada95                       |                                   |

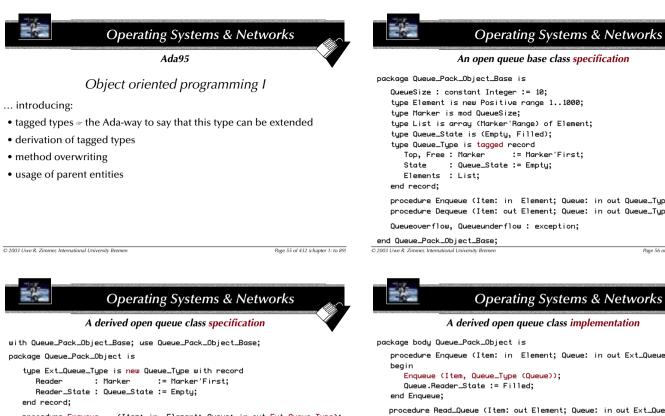

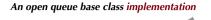

| Object oriented program     | nming II                          |

|                             |                                   |

... introducing:

© 2003 Liwe R. Zimmer Inte

- private tagged types

- objects which are protected against their children also

| <pre>type Element is new Positive range 11000;<br/>type Marker is mod QueueSize;<br/>type List is array (Marker'Range) of Element;<br/>type Queue_State is (Empty, Filled);<br/>type Queue_Type is tagged record<br/>Top, Free : Marker := Marker'First;<br/>State : Queue_State := Empty;<br/>Elements : List;<br/>end record;<br/>procedure Enqueue (Item: in Element; Queue: in out Queue_Type);</pre> | begin<br>if Queue.State = Fil<br>raise Queueoverfil<br>end if;<br>Queue.Elements (Queue<br>Queue.Free := Queue<br>Queue.State := Filler<br>end Enqueue;<br>procedure Dequeue (Item<br>begin<br>if Queue.State := Eis<br>raise Queueu der<br>end if;<br>Item :: Queu.E |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| procedure Dequeue (Item: out Element; Queue: in out Queue_Type);<br>Queueoverflow, Queueunderflow : exception;                                                                                                                                                                                                                                                                                            | Queue.To, := Queue.To<br>if Queue. pp = Queue<br>end Dequeue;                                                                                                                                                                                                         |

| end Queue_Pack_Object_Base;                                                                                                                                                                                                                                                                                                                                                                               | end Queue_Pack_Object_Base                                                                                                                                                                                                                                            |

| Operating Systems & Networks           A derived open queue class implementation                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                       |

| ▼<br>package body Queue_Pack_Object is<br>procedure Enqueue (Item: in Element; Queue: in out Ext_Queue_Type) is                                                                                                                                                                                                                                                                                           | with Queue_Pack_Object_Base<br>with Queue_Pack_Object;<br>with Ada.Text_IO;                                                                                                                                                                                           |

| begin<br>Enqueue (Item, Queue_Type (Queue));                                                                                                                                                                                                                                                                                                                                                              | procedure Queue_Test_Objec                                                                                                                                                                                                                                            |

| Queue.Reader_State := Filled;<br>end Enqueue;                                                                                                                                                                                                                                                                                                                                                             | Queue : Ext_Queue_Type;<br>Item : Element;                                                                                                                                                                                                                            |

| <pre>procedure Read_Queue (Item: out Element; Queue: in out Ext_Queue_Type) is begin     if Queue.Reader_State = Empty then         raise Queueunderflow;     end if;     Item := Queue.Elements (Queue.Reader);     Queue.Reader := Queue.Reader - 1;</pre>                                                                                                                                              | begin<br>Enqueue (Item => 1, Queu<br>Read_Queue (Item, Queue)<br>Enqueue (Item => 5, Queu<br>Dequeue (Item, Queue);<br>Dequeue (Item, Queue);<br>Dequeue (Item, Queue);                                                                                               |

| if Queue.Reader = Queue.Free then Queue.Reader_State := Empty; end if;                                                                                                                                                                                                                                                                                                                                    | exception<br>when Queueunderflow =:<br>when Queueoverflow =:                                                                                                                                                                                                          |

| end Read_Queue;                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                       |

| end Read_Queue;<br>end Queue_Pack_Object;                                                                                                                                                                                                                                                                                                                                                                 | end Queue_Test_Object;                                                                                                                                                                                                                                                |

An encapsulated queue base class specification

package Queue\_Pack\_Object\_Base\_Private is OueueSize : constant Integer := 10; type Element is new Positive range 1..1000; type Queue\_Type is tagged limited private;

procedure Engueue (Item: in Element; Queue: in out Queue\_Type); procedure Dequeue (Item: out Element; Queue: in out Queue\_Type);

Queueoverflow, Queueunderflow : exception;

private

type Marker is mod QueueSize; type List is array (Marker'Range) of Element; type Queue\_State is (Empty, Filled); type Queue\_Type is tagged limited record Top, Free : Marker := Marker'First; State : Queue\_State := Empty; Elements : List; end record:

```

end Queue_Pack_Object_Base_Private;

```

end Queue\_Pack\_Object\_Base\_Private; © 2003 Uwe R. Zimmer, International University Bremen

```

Page 57 of 432 (chapter 1: to 89)

```

|        | 🔛 Оре                                                                                                                                                                 | erating Systems & Networks                                                           |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

|        | An                                                                                                                                                                    | open class test program                                                              |

| wi     | th Queue_Pack_Object_Base<br>th Queue_Pack_Object;<br>th Ada.Text_IO;                                                                                                 | e; use Queue_Pack_Object_Base;<br>use Queue_Pack_Object;<br>use Ada.Text_IO;         |

| pr     | ocedure Queue_Test_Object                                                                                                                                             | t is                                                                                 |

|        | Queue : E×t_Queue_Type;<br>Item : Element;                                                                                                                            |                                                                                      |

| be     | jin<br>Enqueue (Item => 1, Queu<br>Read_Queue (Item, Queue)<br>Enqueue (Item => 5, Queu<br>Dequeue (Item, Queue);<br>Dequeue (Item, Queue);<br>Dequeue (Item, Queue); | );                                                                                   |

|        |                                                                                                                                                                       | > Put ("Queue underflow");<br>> Put ("Queue overflow");                              |

| © 2003 | Uwe R. Zimmer, International University Bremen                                                                                                                        | Page 60 of 432 (chapter                                                              |

|        |                                                                                                                                                                       | erating Systems & Networks<br>ed queue base class implementation                     |

| Þa     | begin                                                                                                                                                                 | in Element; Queue: in out Queu_Type) is<br>led and Queue.Top = Queue Frei the<br>ow; |

procedure Dequeue (Item: out Teme t; Queue: in out Queue\_Type) is

- begin if Queue.State = Eloty then

- raise Quenes ter low; end if;

- Queu. Elements (Queue.Top); Item Queue.To, := Queue.Top - 1;

if Queue. Pp = Queue.Free then Queue.State := Empty; end if; end Dequeue;

```

Page 63 of 432 (chapter 1: to 89)

```

© 2003 Uwe R. Zimmer, International University Bremen

```

Page 62 of 432 (chapter 1: to 89)

```

#### A derived encapsulated queue class specification

with Queue\_Pack\_Object\_Base\_Private; use Queue\_Pack\_Object\_Base\_Private; package Queue\_Pack\_Object\_Private is

tupe Ext\_Queue\_Tupe is new Queue\_Tupe with private: subtupe Depth\_Tupe is Positive range 1..OueueSize:

procedure Look\_Ahead (Item: out Element: Depth: in Depth\_Type; Queue: in out Ext\_Queue\_Type);

private

tupe Ext\_Oueue\_Tupe is new Oueue\_Tupe with null record:

end Queue\_Pack\_Object\_Private;

© 2003 Live R. Zimmer. International University Bremen

**Operating Systems & Networks** An encapsulated class test program with Queue\_Pack\_Object\_Base\_Private; use Queue\_Pack\_Object\_Base\_Private; with Queue\_Pack\_Object\_Private; use Queue\_Pack\_Object\_Private; with Ada.Text\_IO: use Ada.Text\_IO: procedure Queue\_Test\_Object\_Private is Queue : Ext\_Queue\_Type; Item : Element; begin Enqueue (Item => 1, Queue => Queue); Enqueue (Item => 1, Queue => Queue); Look\_Ahead (Item => Item, Depth => 2, Queue => Queue); Enqueue (Item => 5, Queue => Queue); Dequeue (Item, Queue); Dequeue (Item, Queue); Dequeue (Item, Queue); Dequeue (Item, Queue); -- will produce a 'Queue underflow' exception when Queueunderflow => Put ("Queue underflow"); when Queueoverflow => Put ("Queue overflow"); end Queue\_Test\_Object\_Private;

© 2003 Live R. Zimmer, International University Bremen

© 2003 Uwe R. Zimmer. International University Bremen

# **Operating Systems & Networks**

A derived encapsulated queue class implementation

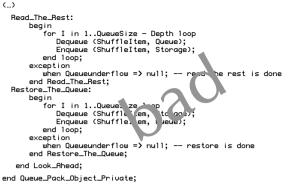

package body Queue\_Pack\_Object\_Private is procedure Look\_Ahead (Item: out Element: Depth: in Depth\_Type; Queue: in out Ext\_Queue\_Type) is Storage : Oueue\_Tupe: ShuffleItem : Element; begin for I in 1..Depth - 1 loop Dequeue (ShuffleItem, Queue); Enqueue (ShuffleItem, Storage); end loop: Dequeue (Item, Queue); Enqueue (Item, Storage); (...)

© 2003 Live R. Zimmer. International University Bremer

**Operating Systems & Networks**

Ada95

Tasks & Monitors

- ... introducing:

- protected types

- tasks (definition, instantiation and termination)

- task synchronisation

- entry guards

- entry calls

- accept and selected accept statements

© 2003 Live R. Zimmer International University Bremer

Page 68 of 432 (chapter 1: to 89)

Page 65 of 432 (chapter 1: to 89)

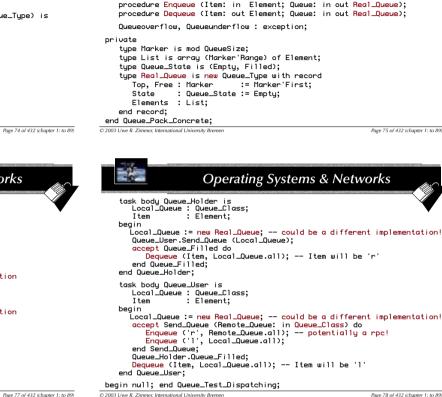

#### A multitasking protected queue test program

with Queue\_Pack\_Protected; use Queue\_Pack\_Protected; with Ada.Text\_IO; use Ada.Text\_IO; procedure Queue\_Test\_Protected is Oueue : Protected\_Oueue: task Producer is entry shutdown; end Producer; task Consumer is end Consumer task body Producer is Item : Element; Got\_It : Boolean; begin 1000 select accept shutdown: exit: -- main task loop else Get\_Immediate (Item, Got\_It); if Got\_It then Queue.Enqueue (Item); -- task might be blocked here! else delay 0.1; --sec. end if: end select; end loop; end Producer; ()Page 71 of 432 (chapter 1: to 89)

**Operating Systems & Networks**

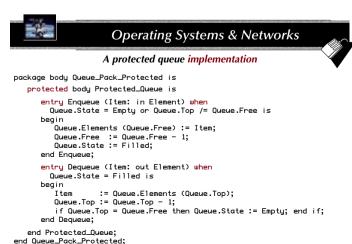

A protected queue specification

Package Queue\_Pack\_Protected is

© 2003 Live R. Zimmer. International University Bremen

QueueSize : constant Integer := 10; subtupe Element is Character: type Queue\_Type is limited private;

Protected type Protected\_Queue is

entru Enqueue (Item: in Element): entry Dequeue (Item: out Element);

private

Queue : Queue\_Type;

end Protected\_Oueue:

private

type Marker is mod QueueSize; type List is array (Marker'Range) of Element; type Queue\_State is (Empty, Filled); type Queue\_Type is record Top, Free : Marker := Marker'First; State : Queue\_State := Empty; Elements : List; end record:

end Queue\_Pack\_Protected; © 2003 Live R. Zimmer, International University Breme

Page 69 of 432 (chapter 1: to 89

Page 66 of 432 (chapter 1: to 89)

# **Operating Systems & Networks**

A multitasking protected queue test program (cont.)

(...)

task bodu Consumer is

Item : Element:

beain

1000

Queue.Dequeue (Item); -- task might be blocked here!

Put ("Received: "); Put (Item); Put⊥ine ("!");

- if Item = 'q' then

- Put\_Line ("Shutting down producer"); Producer.Shutdown;

- Put⊥ine ("Shutting down consumer"); exit; -- main task loop

- end if: end loop:

end Consumer;

beain

null

end Oueue\_Test\_Protected: © 2003 Uwe R. Zimmer. International University Bremen

Page 64 of 432 (chapter 1: to 89)

Page 67 of 432 (chapter 1: to 89)

© 2003 Uwe R. Zimmer. International University Bremen

Ada95

#### Abstract types & dispatching

- ... introducing:

- abstract tagged types

- abstract subroutines

- concrete implementation of abstract types

- dispatching to different packages, tasks, and partitions according to concrete types

#### **Operating Systems & Networks**

#### An abstract queue specification

- package Queue\_Pack\_Abstract is

- subtype Element is Character;

- type Queue\_Type is abstract tagged limited private;

- procedure Enqueue (Item: in Element; Queue: in out Queue\_Type) is abstract;

- procedure Dequeue (Item: out Element; Queue: in out Queue\_Type) is abstract;

private

type Queue\_Type is abstract tagged limited null record; end Queue\_Pack\_Abstract;

© 2003 Uwe R. Zimmer, International University Bremen

Page 73 of 432 (chapter 1: to 89) © 2003 Uwe R. Zimmer, International University Bremen

#### Ada95 language status

- Established language standard with free and commercial compilers available for all major OSs.

- Stand-alone runtime environments for embedded systems (some are only available commercially).

- Special (yet non-standard) extensions (i.e. language reductions and proof systems) for extreme small footprint embedded systems or high integrity real-time environments available - Ravenscar profile systems.

- has been used and is in use in numberless large scale projects

(e.g. in the international space station, and in some spectacular crashes: e.g. Ariane 5)

## **Operating Systems & Networks**

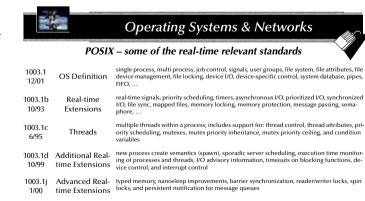

POSIX

Portable Operating System Interface for Computing Environments

- IEEE/ANSI Std 1003.1 and following

- Program Interface (API) [C Language]

- more than 30 different POSIX standards (a system is 'POSIX compliant', if it implements parts of just one of them!)

**Operating Systems & Networks**

A concrete queue specification

with Oueue\_Pack\_Abstract: use Oueue\_Pack\_Abstract:

type Real\_Queue is new Queue\_Type with private;

OueueSize : constant Integer := 10:

package Queue\_Pack\_Concrete is

1003.21

Distributed Real-time

buffer management, send control blocks, asynchronous and synchronous operations, bounded blocking, message priorities, message labels, and implementation protocols

© 2003 Uwe R. Zimmer, International University Bremen

© 2003 Uwe R. Zimmer, International University Bremen

Page 80 of 432 (chapter 1: to 89) © 2003 Uwe R. Zimmer, International University Bremen

#### POSIX - 1003.1b

## Frequently employed POSIX features include:

- Timers: delivery is accomplished using POSIX signals

- Priority scheduling: fixed priority, 32 priority levels

- Real-time signals: signals with multiple levels of priority

- Semaphore: named semaphore

© 2003 Live R. Zimmer. International University Bremen

- Memory queues: message passing using named queues

- · Shared memory: memory regions shared between multiple processes

- Memory locking: no virtual memory swapping of physical memory pages

#### Page 82 of 432 (chapter 1: to 89)

## **Operating Systems & Networks**

#### POSIX – example: setting a timer

void timer\_create(int num\_secs, int num\_nsecs)

struct sigaction sa: struct sigevent sig\_spec; sigset\_t allsigs; struct itimerspec tmr\_setting; timer\_t timer\_h; /\* setup signal to respond to timer \*/ sigemptyset(&sa.sa\_mask); sa.sa\_flags = SA\_SIGINF0; sa.sa\_sigaction = timer\_intr; if (sigaction(SIGRTMIN, &sa, NULL) < 0) perror('sigaction'); sig\_spec.sigev\_notify = SIGEV\_SIGNAL; sig\_spec.sigev\_signo = SIGRTMIN;

© 2003 Uwe R. Zimmer, International University Bremen

© 2003 Uwe R. Zimmer. International University Bremen

## **Operating Systems & Networks**

#### Languages

## Languages used in this course

|                                      | Ada                                | RT-Java   | C/C++                              | Posix                       |  |  |

|--------------------------------------|------------------------------------|-----------|------------------------------------|-----------------------------|--|--|

| Predictability                       | ***<br>(specific<br>run-time env.) | <br>(OOP) | implementation<br>dependent        | implementation<br>dependent |  |  |

| low-level interfaces                 | ***                                | -         | **                                 | **                          |  |  |

| Concurrency                          | ***                                | **        |                                    | **                          |  |  |

| Distribution                         | **                                 | ***       |                                    | *                           |  |  |

| Error detection<br>(compiler, tools) | **<br>(strong typing)              | **        |                                    |                             |  |  |

| Large systems                        | ***                                | ***       | OOP C++ style<br>(no support in C) | /                           |  |  |

|                 | POSIX 1003.1<br>(Base POSIX)                 | POSIX 1003.1b<br>(Real-time<br>extensions)           | POSIX 1003.1c<br>(Threads)               |  |  |  |  |

|-----------------|----------------------------------------------|------------------------------------------------------|------------------------------------------|--|--|--|--|

| Solaris         | Full support                                 | Full support                                         | Full support                             |  |  |  |  |

| IRIX            | Conformant                                   | Full support                                         | Full support                             |  |  |  |  |

| LynxOS          | Conformant                                   | Full support                                         | Conformant (Version 3.1)                 |  |  |  |  |

| QNX<br>Neutrino | Full support                                 | Partial support<br>(no memory locking)               | Full support                             |  |  |  |  |

| Linux           | Full support                                 | Partial support<br>(no timers,<br>no message queues) | Full support                             |  |  |  |  |

| VxWorks         | Partial support<br>(different process model) | Partial support<br>(different process model)         | Supported through third<br>party product |  |  |  |  |

POSIX – support in some OSs

**Operating Systems & Networks**

# **Operating Systems & Networks**

#### POSIX – example: setting a timer (cont.)

/\* create timer, which uses the REALTIME clock \*/ if (timer\_create(CLOCK\_REALTIME, &sig\_spec, &timer\_h) < 0) perror('timer create');

/\* set the initial expiration and frequency of timer \*/ tmr\_setting.it\_value.tv\_sec = 1;

- tmr\_setting.it\_value.tv\_nsec = 0;

- tmr\_setting.it\_interval.tv\_sec = num\_secs;

tmr\_setting.it\_interval.tv\_sec = num\_nsecs; if ( timer\_settime(timer\_h, 0, &tmr\_setting,NULL) < 0) perror('settimer'):

/\* wait for signals \*/ sigemptyset(&ailsigs); while (1) {

sigsuspend(&allsigs);

/\* routine that is called when timer expires \*/ void timer\_intr(int sig, siginfo\_t \*extra, void \*cruft)

/\* perform periodic processing and then exit \*/

Page 85 of 432 (chapter 1: to 89

## **Operating Systems & Networks**

Summary

#### Introduction to operating systems

- · Features (and non-features) of operating system

- · Common grounds for operating systems

- Historical perspectives

- · Types of current operating systems

- · Design principles for system software (monoliths & µkernels)

- · Examples of languages considered for system level programming:

- Java

- Ada95

- POSIX interfaces

- C/C++

}

# **Operating Systems & Networks**

**POSIX** – other languages

## POSIX is a 'C' standard ...

- ... but **bindings to other languages** are also (suggested) POSIX standards:

- Ada: 1003.5\*, 1003.24 (some PAR approved only, some withdrawn)

- Fortran: 1003.9 (6/92)

- Fortran90: 1003.19 (withdrawn)

- ... and there are POSIX standards for task-specific POSIX profiles, e.g.:

- Super computing: 1003.10 (6/95)

- Realtime: 1003.13, 1003.13b (3/98)

- profiles 51-54: combinations of the above RT-relevant POSIX standards or RT-Linux

- Embedded Systems: 1003.13a (PAR approved only)

- © 2003 Uwe R. Zimmer, International University Bremen

# **Operating Systems & Networks**

Page 84 of 432 (chapter 1: to 89)

#### POSIX – example: setting a timer (cont.)

```

/* create timer, which uses the REALTIME clock */

if (timer_create(CLOCK_REALTIME, &sig_spec, &timer_h) < 0)

perror('timer create'):

/* set the initial expiration and frequency of timer */

tmr_setting.it_value.tv_sec = 1;

tmr_setting.it_value.tv_nsec = 0;

tmr_setting.it_interval.tv_sec = num_secs;

tmr_setting.it_interval.tv_sec = num_nsecs;

ine (1) { remember the Pearl timers(

sigsuspend(&alls <sub>AFTER</sub> 30 HIN ALL 5 HIN DURING 1 HAS ACTIVATE Help;

remember the Pearl timers?

if ( timer_settime(timer_h, 0, &tmr_setting,NULL) '

/* wait for signals */

sigemptyset(&allsigs)

while (1) {

/* routine that is called when timer expires */

void timer_intr(int sig, siginfo_t *extra, void *cruft)

```

/\* perform periodic processing and then exit \*/

Hardware Fundamentals Uwe R. Zimmer – International University Bremen

Page 89 of 432 (chapter 1: to 89)

#### References for this chapter

[Silberschatz01] – Chapter 2 Abraham Silberschatz, Peter Bear Galvin, Greg Gagne Operating System Concepts John Wiley & Sons, Inc., 2001

[Stallings2001] – Chapter 1 William Stallings Operating Systems Prentice Hall, 2001

all references and some links are available on the course page

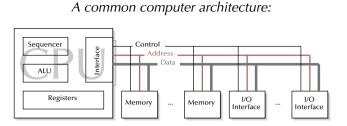

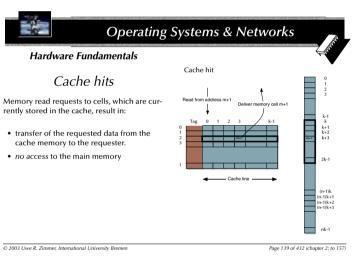

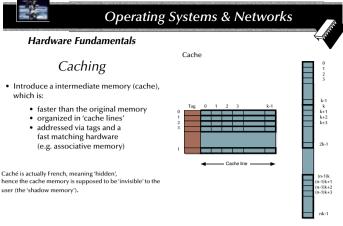

Hardware Fundamentals

**Operating Systems & Networks**

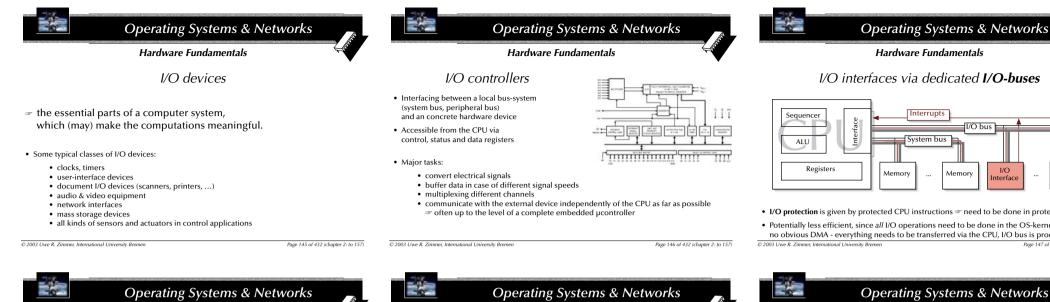

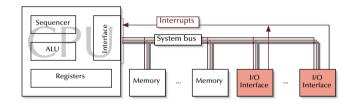

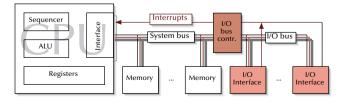

Bus-systems carry device, address information and data (8-64 bit wide) as well as control lines in groups such as: · arbitration, synchronization, requests, interrupts, priorities

© 2003 Uwe R. Zimmer, International University Bremen

© 2003 Live R. Zimmer. International University Bremen

© 2003 Uwe R. Zimmer. International University Bremen

Page 91 of 432 (chapter 2: to 157)

Page 94 of 432 (chapter 2: to 157)

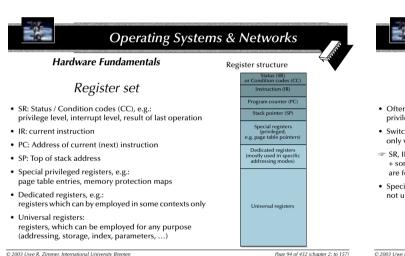

| 41=F                                                                                                                                                                   |                |                                                                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------------------------------------------------------------------------|

| Operating System                                                                                                                                                       | 15 &           | Networks                                                                             |

| Hardware Fundamentals                                                                                                                                                  | Re             | gister structure                                                                     |

| Often divided into a                                                                                                                                                   | Privileged     | Status (SR)<br>or Condition codes (CC)<br>Instruction (IR)<br>Program counter (PC)   |

| <ul> <li>Switch from non-privileged section</li> <li>Switch from non-privileged to privileged mode<br/>only via traps or interrupts (later in this chapter)</li> </ul> | Privil         | Stack pointer (SP)<br>Special registers<br>(privileged,<br>e.g. page table pointers) |

| SR, IR, PC, SP<br>+ some general registers (or at least one 'accumulator')<br>are found in all current processor designs                                               | q              | Dedicated registers<br>(mostly used in specific<br>addressing modes)                 |

| <ul> <li>Special and dedicated registers are<br/>not used in all architectures</li> </ul>                                                                              | Non-privileged | Universal registers                                                                  |

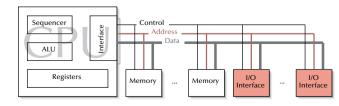

Seauence Control Address Data ALU Registers 1/0 Memo Memory Interface

#### CPU components relevant for this course;

© 2003 Live R. Zimmer. International University Bremen

register-set, sequencer ('normal operation'), interrupt controller, protected modes

Asynchronism

Interrupts

• Interrupt control: grouping, encoding, prioritising, and en-/disabling interrupt sources

• Context switching: mechanisms for cpu-state saving and restoring + task-switching

Required mechanisms for interrupt driven programming:

• Interrupt identification: Interrupt vectors, interrupt states

**Operating Systems & Networks**

Hardware Fundamentals

The CPU

Page 93 of 432 (chapter 2: to 157)

I/O

Interface

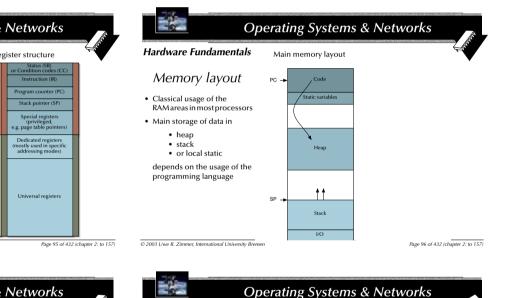

#### **Operating Systems & Networks** Hardware Fundamentals Main memory layout † † Stack frames PC -Return add Static variables Context reference · Every sub-program call leaves an entry on the stack with all relevant information: parameters Local variables • context (not in 'C') Heap · return address Saved environment · Parameters may Return address he removed by: Context refere the calling routine ('C') **† †** · or the called routine Return addres SP Special architectures Context reference Stack support faster parameter passing (e.g. register-bands) I/O

Page 97 of 432 (chapter 2: to 157)

**Operating Systems & Networks**

#### Hardware Fundamentals

#### Privileged instructions

#### Purpose:

- · prevent user level tasks from by-passing the operating system

- · restrict access form user-level tasks to resources, which are managed by the operating system:

- Memory

© 2003 Live & Zimmer International Liniversity Bremer

- I/O

- · Structures which are used to administer memory or I/O access (e.g. special registers, MMUs, etc.)

#### Implementation:

- · declare some instructions privileged

- · implement two (or more) protection levels in the CPU

- · allow changes to a higher privilege level by means of traps/exceptions/interrupts only.

© 2003 Uwe R. Zimmer, International University Bremen

Page 98 of 432 (chapter 2: to 157) © 2003 Uwe R. Zimmer. International University Bremen

In hardware-supported

Page 92 of 432 (chapter 2: to 157)

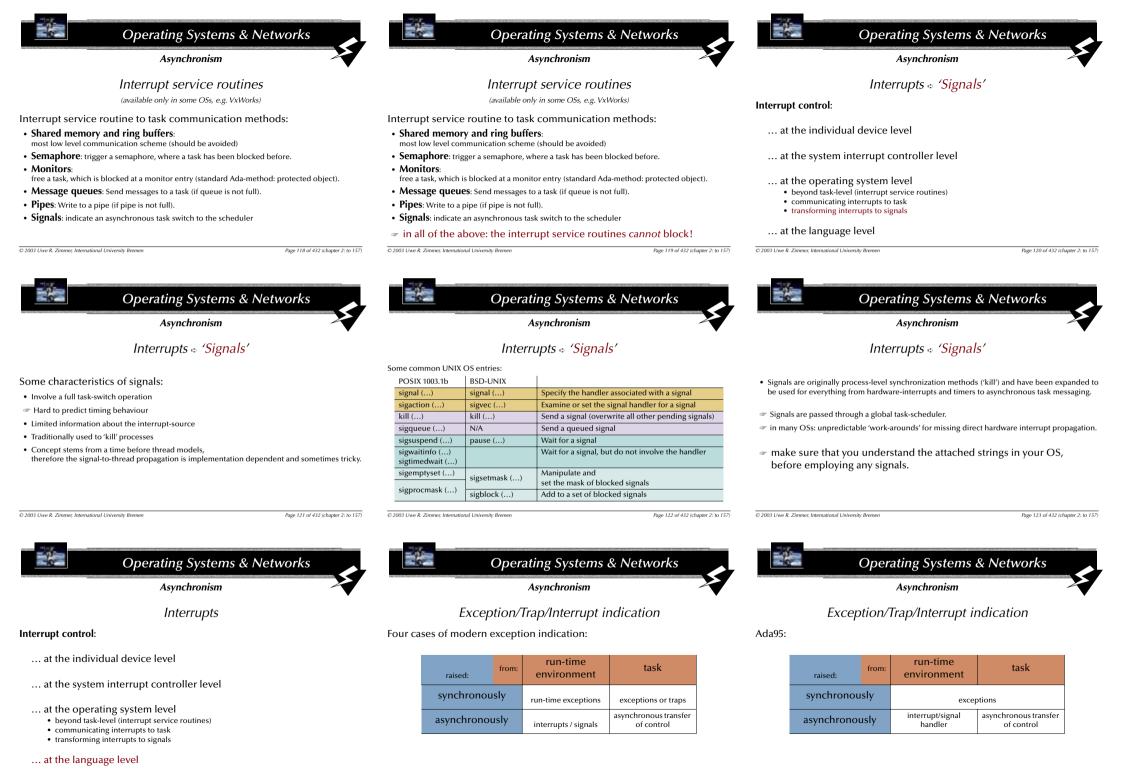

#### Asynchronism

#### Interrupts

#### Interrupt control:

#### ... at the individual device level

#### ... at the system interrupt controller level

- ... at the operating system level

- beyond task-level (interrupt service routines)

- · communicating interrupts to task

- · transforming interrupts to signals

#### ... at the language level

© 2003 Live R. Zimmer. International University Bremen

#### Page 100 of 432 (chapter 2: to 157)

Page 106 of 432 (chapter 2: to 157)

# **Operating Systems & Networks**

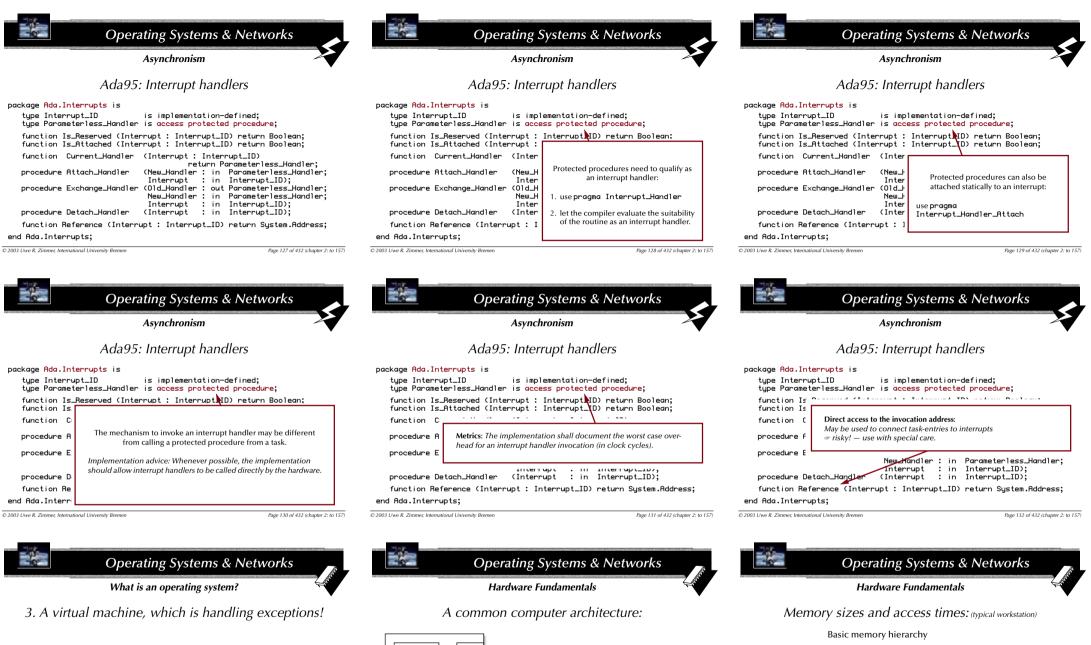

|    | LM12L458 – accessible registers |    |    |                    |      |     |                       |          |         |                |         |          |      |       |           |       |          |           |       |       |       |

|----|---------------------------------|----|----|--------------------|------|-----|-----------------------|----------|---------|----------------|---------|----------|------|-------|-----------|-------|----------|-----------|-------|-------|-------|

| A4 | A3                              | A2 | A1 | Purpose            | Туре | D15 | D14                   | 4 D13    | D12     | D11            | D10     | D9       | D8   | D7    | D6        | D5    | D4       | D3        | D2    | D1    | D0    |

|    | 0                               | 0  | 0  | Instruction RAM    | R/W  |     | Acq                   | uisition | 1       | Watch-         |         |          |      |       |           |       |          |           |       |       |       |

| 0  |                                 | to |    | (RAM Pointer = 00) |      |     | Time dog 8/           |          |         |                |         | Timer    | Sync |       | $V_{IN-}$ |       |          | $V_{IN+}$ |       | Pause | Loop  |

|    | 1                               | 1  | 1  |                    |      |     |                       |          |         |                |         |          |      |       |           |       |          |           |       |       |       |

|    | 0                               | 0  | 0  | Instruction RAM    | R/W  |     |                       |          |         |                |         |          |      |       |           |       |          |           |       |       |       |

| 0  |                                 | to |    | (RAM Pointer = 01) |      |     |                       |          | Don't   | Care           |         | >/<      | Sign |       |           |       | Lim      | iit #1    |       |       |       |

|    | 1                               | 1  | 1  |                    |      |     |                       |          |         |                |         |          |      |       |           |       |          |           |       |       |       |

|    | 0                               | 0  | 0  | Instruction RAM    | R/W  | RW  |                       |          |         |                |         |          |      |       |           |       |          |           |       |       |       |

| 0  |                                 | to |    | (RAM Pointer = 10) |      |     |                       |          | Don't   | Care           |         | >/<      | Sign |       |           |       | Lim      | iit #2    |       |       |       |

|    | 1                               | 1  | 1  |                    |      |     |                       |          |         |                |         |          |      |       |           |       |          |           |       |       |       |

| 1  | 0                               | 0  | 0  | Configuration      | R/W  |     | Don't Care DIAG       |          |         |                | Test    | R        | RAM  |       | Auto      | Chan  | Stand-   | Full      | Auto- | Reset | Start |

|    |                                 |    |    | Register           |      |     |                       |          |         |                | = 0     | Pointer  |      | Sel   | Zeroec    | Mask  | by       | CAL       | Zero  |       |       |

|    |                                 |    |    | Interrupt Enable   | R/W  |     | Number of Conversions |          |         |                |         | equend   | ber  | INT7  | Don't     | INT5  | INT4     | INT3      | INT2  | INT1  | INTO  |

| 1  | 0                               | 0  | 1  | Register           |      |     | in                    | Conv     | ersion  | FIFO           | 1       | ddress   | to   |       | Care      |       |          |           |       |       |       |

|    |                                 |    |    |                    |      |     | 1                     | to Gen   | erate I | NT2            | Ge      | nerate   | INT1 |       |           |       |          |           |       |       |       |

|    |                                 |    |    |                    |      |     |                       |          |         |                |         | Addres   | 8    |       |           |       |          |           |       |       |       |

|    |                                 |    |    |                    | R    |     |                       | Actual   | Numb    | er of          |         | of       |      | INST7 | -0-       | INST5 | INST4    | INST3     | INST2 | INST1 | INST  |

| 1  | 0                               | 1  | 0  | Interrupt Status   |      |     | С                     | onvers   | ion R   | sults          | s       | equend   | ber  |       |           |       |          |           |       |       |       |

|    |                                 |    |    | Register           |      |     | ir                    | Conv     | ersion  | FIFO           | 1       | nstructi | on   |       |           |       |          |           |       |       |       |

|    |                                 |    |    |                    |      |     |                       |          |         |                |         | being    |      |       |           |       |          |           |       |       |       |

|    |                                 |    |    |                    |      |     |                       |          |         |                |         | Execute  | d    |       |           |       |          |           |       |       |       |

| 1  | 0                               | 1  | 1  | Timer              | R/W  |     |                       |          | Time    | Preset High    | Byte    |          |      |       |           | Tim   | her Pres | et Low    | Byte  |       |       |

|    |                                 |    |    | Register           |      |     |                       |          |         |                |         |          |      |       |           |       |          |           |       |       |       |

| 1  | 1                               | 0  | 0  | Conversion         | R    |     | Addre                 | 168      | Sign    |                | Convers | ion      |      |       |           | Cor   | version  | Data: L   | SBs   |       |       |

|    |                                 |    |    | FIFO               |      |     | or Si                 | gn       |         | 1              | ata: M  | SBs      |      |       |           |       |          |           |       |       |       |

| 1  | 1                               | 0  | 1  | Limit Status       | R    |     |                       | -        | L       | imit #2: Statu | 3       |          |      |       |           |       | Limit #  | 1: Statu  |       |       |       |

|    |                                 |    |    | Register           |      |     |                       |          |         |                |         |          |      |       |           |       |          |           |       |       |       |

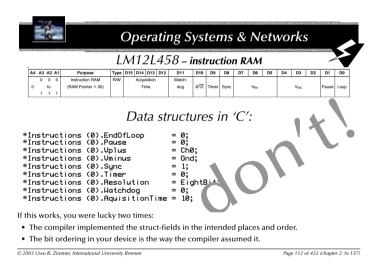

#### **Operating Systems & Networks** LM12L458 – instruction RAM Type D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 A4 A3 A2 A1 Purpose Instruction RAM 8/12 (RAM Pointer = 00) Time dog V<sub>IN4</sub> type ChannelPlus is (Ch0, Ch1, Ch2, Ch3, Ch4, Ch5, Ch6, Ch7); type ChannelMinus is (Gnd, Ch1, Ch2, Ch3, Ch4, Ch5, Ch6, Ch7); type Resolutions is (TwelveBit, EightBit); type Aquisition\_D is new Integer range 0..15; -- 9+2D (12bit), 2+2D (8bit) for ChannelPlus use (Ch0 => 0, Ch1 => 1, Ch2 => 2, Ch3 => 3, Ch4 => 4, Ch5 => 5, Ch6 => 6, Ch7 => 7; for ChannelMinus use (Gnd => 0, Ch1 => 1, Ch2 => 2, Ch3 => 3, Ch4 = 4, Ch5 = 5, Ch6 = 6, Ch7 = 7; for Resolutions use (TwelveBit => 0, EightBit => 1); tupe Instruction is record EndOfLoop, Pause, Sync, Timer, Watchdog : Boolean; Vplus ChannelPlus; . Vminus ChannelMinus; Resolution Resolutions; AquisitionTime : Aquisition D:

#### © 2003 Uwe R. Zimmer. International University Bremen

**Operating Systems & Networks**

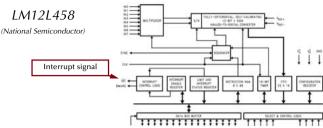

# Interrupts

#### only one interrupt signal line available!

in order to identify the interrupt reason, an additional read cycle is required!

© 2003 L/we R Zimmer International University Bremen

Page 101 of 432 (chapter 2: to 157)

Page 104 of 432 (chapter 2: to 157)

#### **Operating Systems & Networks** 111121158 instruction RAM

|    | LIVITZL430 – Instruction KAM |     |    |    |                    |      |                              |             |        |     |         |        |      |      |      |    |                  |    |     |       |      |    |    |

|----|------------------------------|-----|----|----|--------------------|------|------------------------------|-------------|--------|-----|---------|--------|------|------|------|----|------------------|----|-----|-------|------|----|----|

| A4 | A                            | 3 A | 12 | A1 | Purpose            | Type | D15                          | D           | 14 E   | 13  | D12     | D11    | D10  | D9   | D8   | D7 | D6               | D5 | D4  | D3    | D2   | D1 | D0 |

|    | 0                            | 1   | 0  | 0  | Instruction RAM    | R/W  |                              | A           | cquisi | ion |         | Watch- |      |      |      |    |                  |    |     |       |      |    |    |

| 0  |                              | b   | 0  |    | (RAM Pointer = 00) |      |                              | Time dog 8/ |        |     | 8/12    | Timer  | Sync | VIN- |      |    | V <sub>IN+</sub> |    |     | Pause | Loop |    |    |

|    | 1                            | 1   | 1  | 1  |                    |      |                              |             |        |     |         |        |      |      |      |    |                  |    |     |       |      |    |    |

|    | 0                            | -   | 0  | 0  | Instruction RAM    | R/W  |                              |             |        |     |         |        |      |      |      |    |                  |    |     |       |      |    |    |

| 0  |                              | b   | 0  |    | (RAM Pointer = 01) |      |                              |             |        | E   | Don't ( | Care   |      | >/<  | Sign |    |                  |    | Lim | it #1 |      |    |    |

|    | 1                            |     | 1  | 1  |                    |      |                              |             |        |     |         |        |      |      |      |    |                  |    |     |       |      |    |    |

|    | 0                            | -   | 0  | 0  | Instruction RAM    | R/W  |                              |             |        |     |         |        |      |      |      |    |                  |    |     |       |      |    |    |

| 0  |                              | b   | 0  |    | (RAM Pointer = 10) |      | Don't Care >/< Sign Limit #2 |             |        |     |         |        |      |      |      |    |                  |    |     |       |      |    |    |

|    | 1                            |     | 1  | 1  |                    |      |                              |             |        |     |         |        |      |      |      |    |                  |    |     |       |      |    |    |

#### every entry in the instruction RAM consists of:

- Loop (1bit): indicates the last instruction and branches to the first one.

- Pause (1bit): halts the sequencer before this instruction

- V<sub>IN+</sub>, V<sub>IN-</sub> (2\*3 bit): select the input channels (000 selects ground in V<sub>IN-</sub>)

# A4

#### Units\_Per\_Word : constant Integer := Word\_Size / Storage\_Unit;

#### for Instruction use record

© 2003 Uwe R. Zimmer, International University Bremen

|                |    | u                |       |       |

|----------------|----|------------------|-------|-------|

| End0fLoop      | at | 0*Units_Per_Word | range | 0 0;  |

| Pause          | at | 0*Units_Per_Word | range | 1 1;  |

| Vplus          | at | 0*Units_Per_Word | range | 24;   |

| Vminus         | at | 0*Units_Per_Word | range | 5 7;  |

| Sync           | at | 0*Units_Per_Word | range | 8 8;  |

| Timer          | at | 0*Units_Per_Word | range | 99;   |

| Resolution     | at | 0*Units_Per_Word | range | 1010; |

| Watchdog       | at | 0*Units_Per_Word | range | 1111; |

| AquisitionTime | at | 0*Units_Per_Word | range | 1215; |

| end record;    |    |                  |       |       |

## **Operating Systems & Networks**

A/D, D/A & Interfaces

#### LM12L458

12-Bit + sign, 8 channel, A/D converter, controller and interface

#### **Controller features:**

- Programmable acquisition times and conversion rates

- 32-word conversion FIFO

- Self-calibration and diagnostic mode

- 8- or 16-bit wide data bus microprocessor or DSP

#### Typ. applications:

- Data Logging

- Process Control

© 2003 Liwe R. Zimmer. International University Bremen

© 2003 Uwe R. Zimmer. International University Bremen

Page 102 of 432 (chapter 2: to 157)

|    | ALC: NOT ALC | No.            |      |                    |      | Operati         | 0      | ,    |       |      |    |                  |    | vo  |           |    |       |     |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------|--------------------|------|-----------------|--------|------|-------|------|----|------------------|----|-----|-----------|----|-------|-----|

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | and the second | 5.54 |                    |      | M12L4           |        |      |       |      |    |                  |    |     |           |    | _     |     |

| A4 | A3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | A2             | A1   | Purpose            | Type | D15 D14 D13 D12 | D11    | D10  | D9    | D8   | D7 | D6               | D5 | D4  | D3        | D2 | D1    | D0  |