# Operating System & Networks 2003 Uwe R. Zimmer – International University Bremen

#### what is offered here?

Overviews, Paths, Definitions, Terminology, Foundations, Methods, Algorithms Realities, Current research trends, Projects, Perspectives, ... and some theory

### into/for/about Operating Systems & Networks

who could be interested in this?

anybody who ...

... would like to see

how rich, diverse and deep the real world of operating systems goes

... would like to learn how to create predictability and fault-tolerant operating systems

... would like to know more about the usage of 95% of all µprocessors (and thus operating systems)

#### who are these people? – introduction

#### This course will be given by

### Holger Kenn for the networks sections

#### and

Uwe R. Zimmer for the operating systems sections

#### how will this all be done?

- Lectures (320-202):

- 2 per week ... all the nice stuff and theory Tuesday, 8:00-9:15; Friday, 11-12:15 – all in Conrad Naber lecture hall

- Labs (Advanced CS lab), independent course, but related (320-222):

- 2 sessions per week ... all the rough stuff and practice Monday 15:30-19:30; Tuesday 15:30-19:30

- Resources:

- introduced in the lectures and collected on the course page: http://www.faculty.iu-bremen.de/course/FundCS2/

... as well as schedules, slides, code, etc. pp. ... keep an eye on these pages!

- Assessment:

- Two exams, 50% each, one oral exam, one written exam assignments for self-checking

Topics in operating systems

- 1. Introduction

- 2. Hardware basics

- 3. Processes

- 4. Memory management

### Table of contents

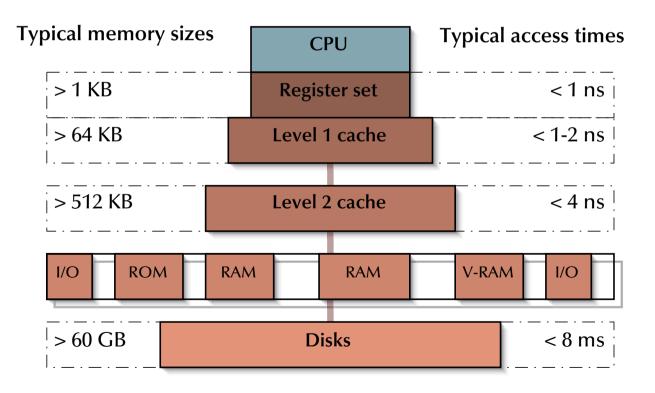

### 2. Hardware Fundamentals

- General computer architecture

- CPU

- Registers

- Traps/Interrupts & protected modes

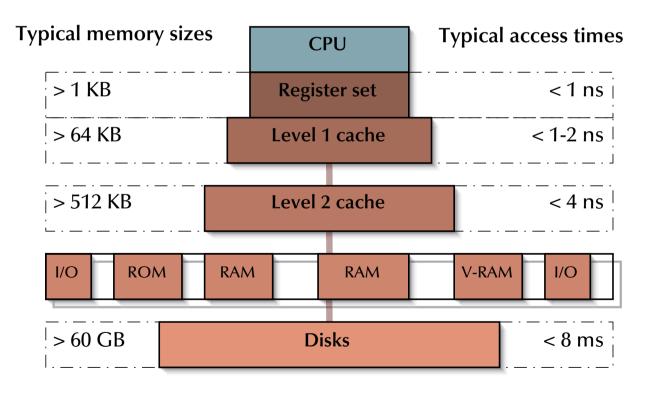

- Memory

- General memory layout

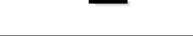

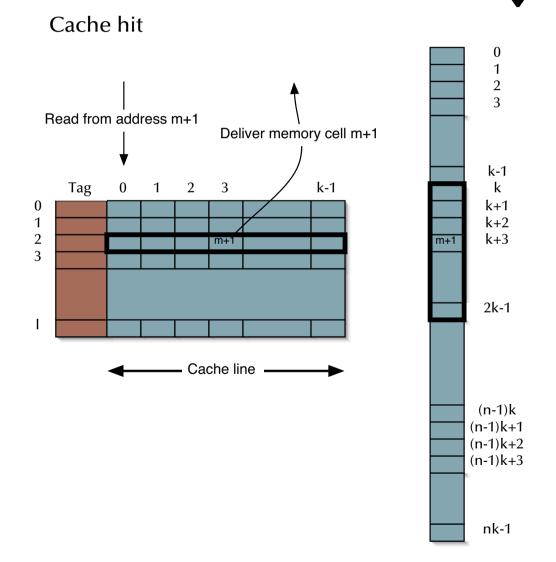

- Caching

- I/O systems

- I/O controllers, I/O buses, device programming

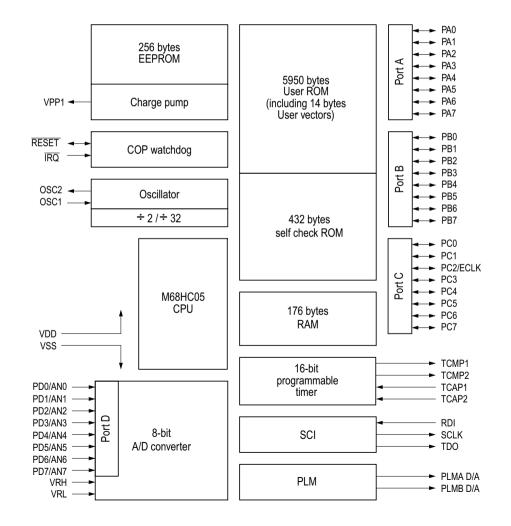

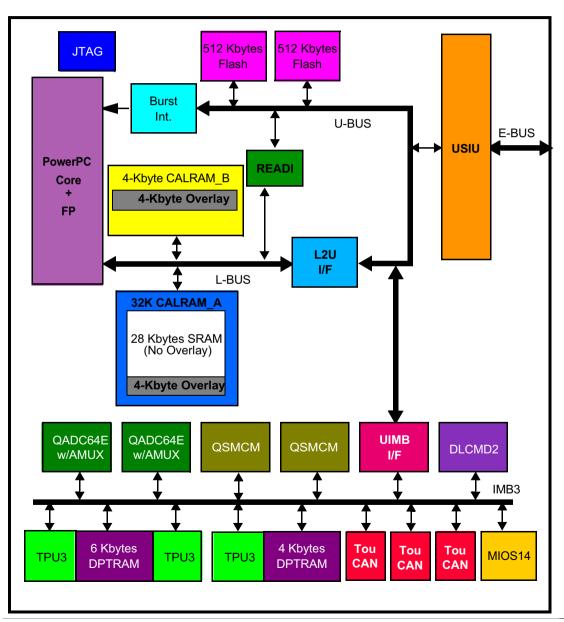

- Some examples of µprocessors

- Small scale µcontroller (68HC05)

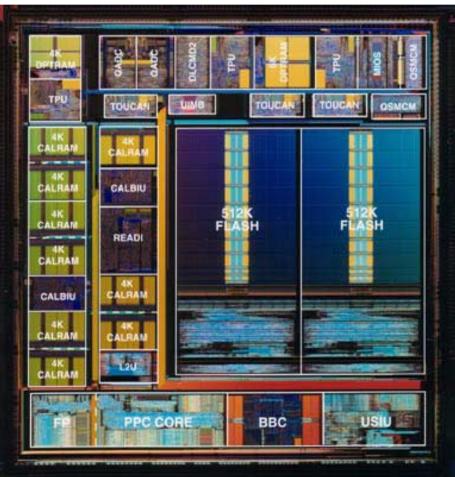

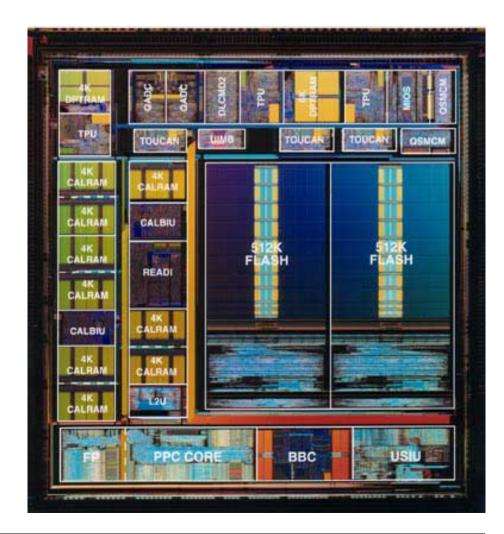

- Full scale integrated processor (MCP565)

#### Table of contents

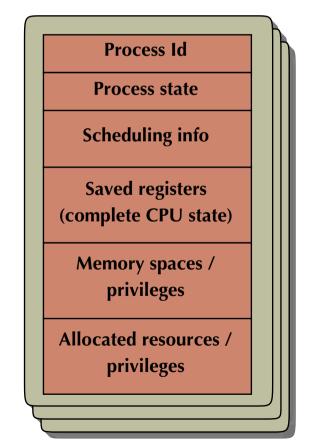

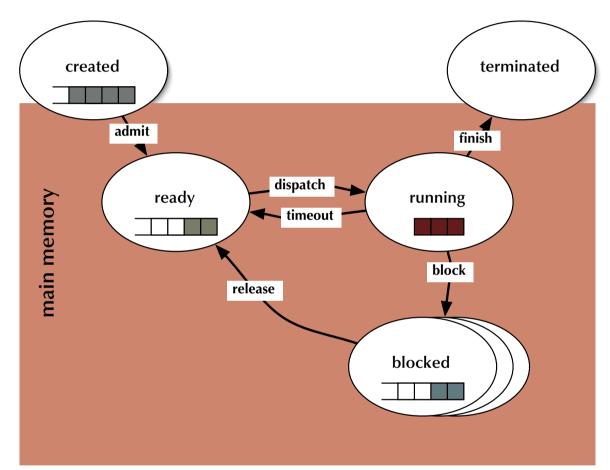

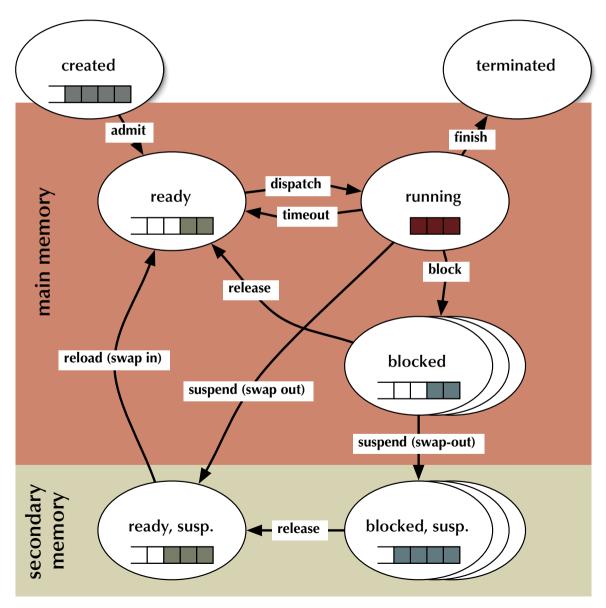

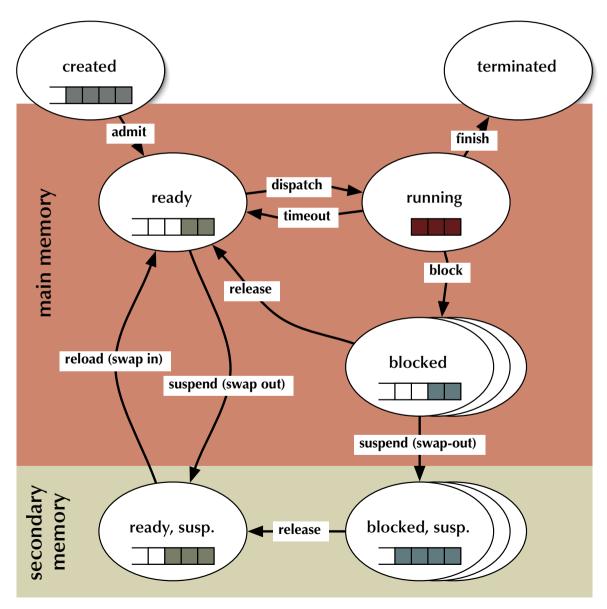

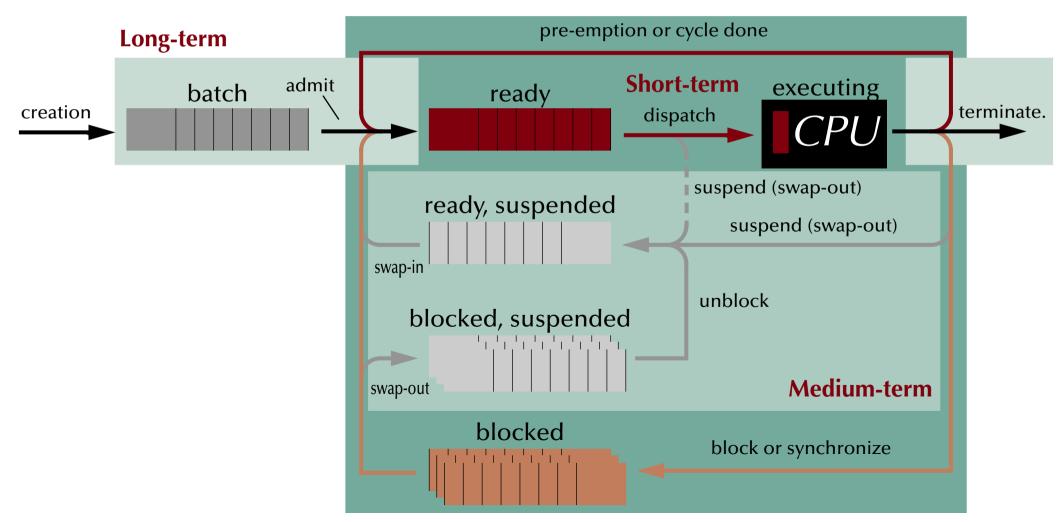

### 3. Processes

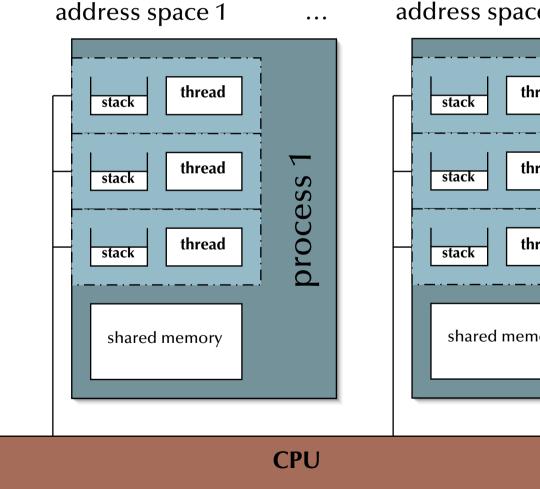

- Processes and threads

- Architectures, definitions, process states

- Synchronization

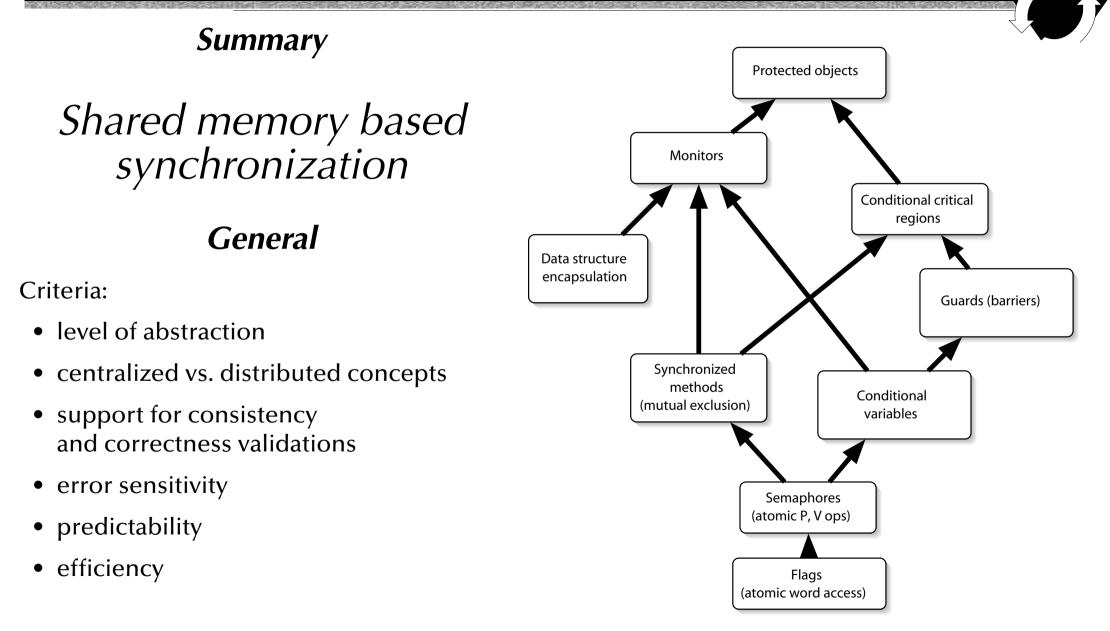

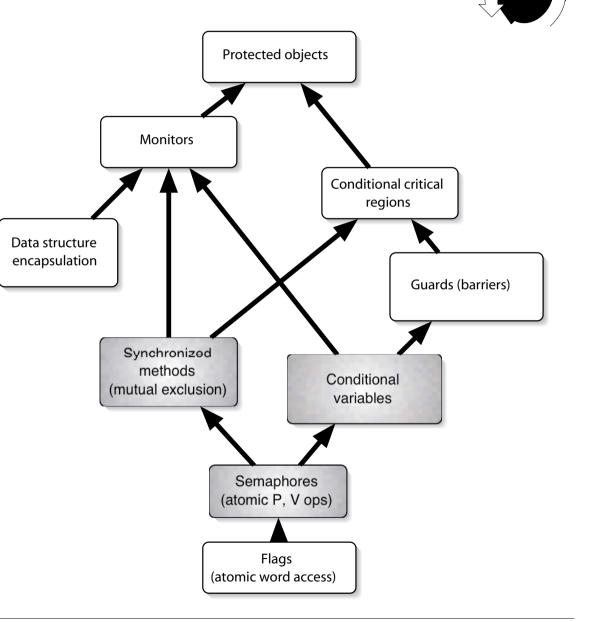

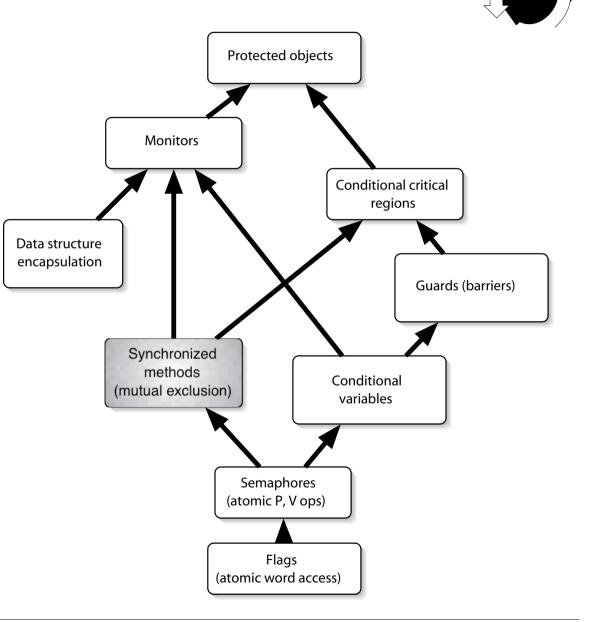

- Shared memory based synchronization

- Message based synchronization

- Deadlocks

- Detection, avoidance, and prevention (& recovery)

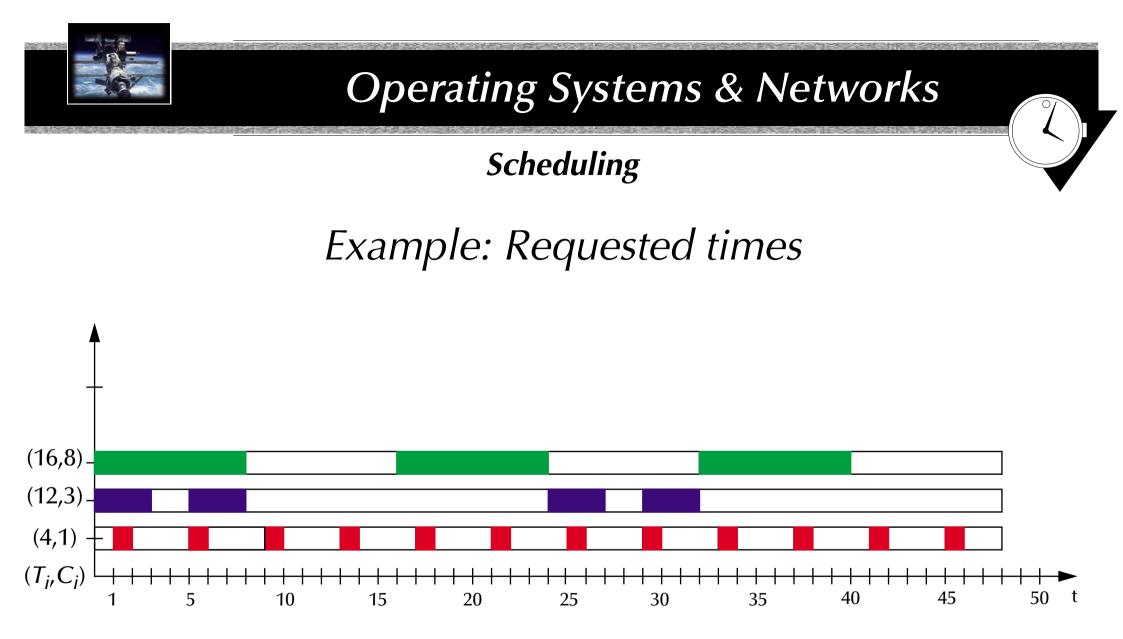

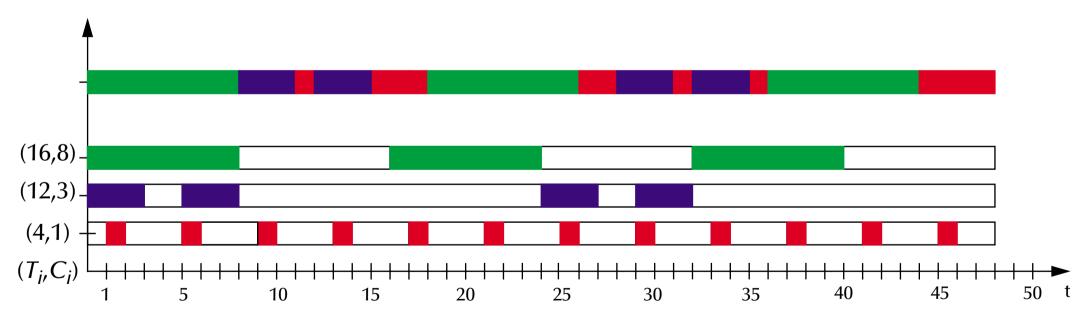

- Scheduling

- Basic performance based scheduling

- Basic predictable scheduling

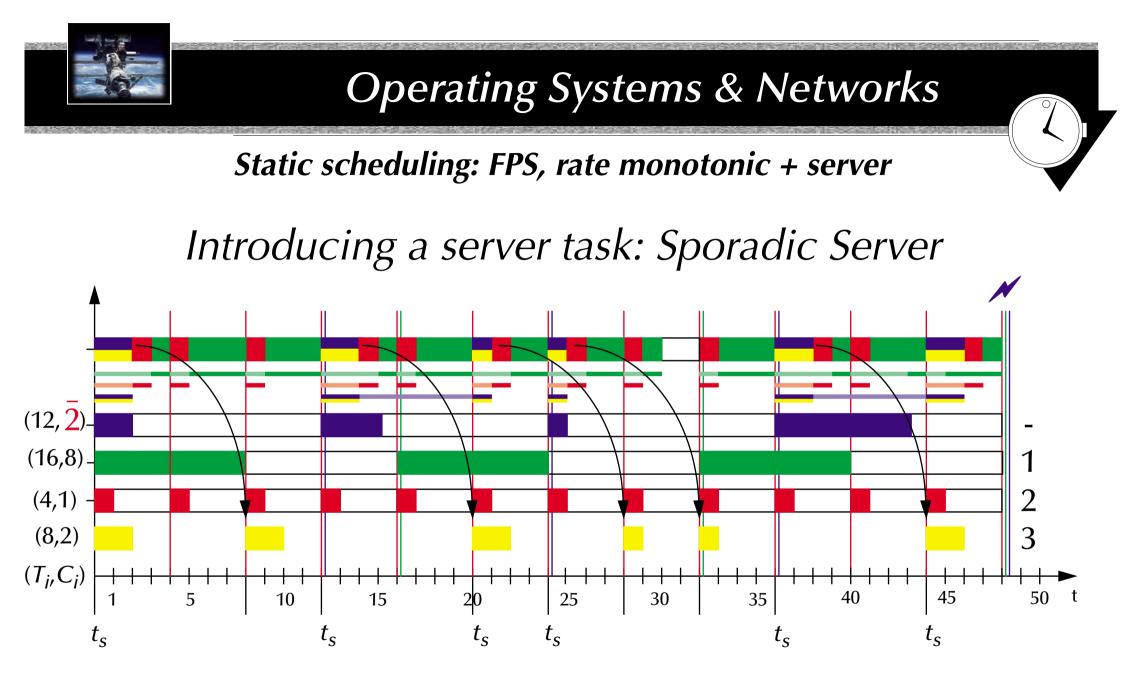

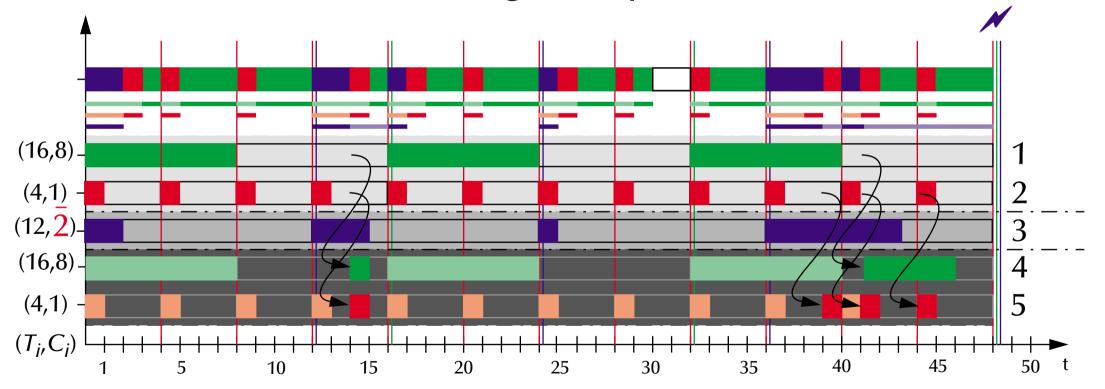

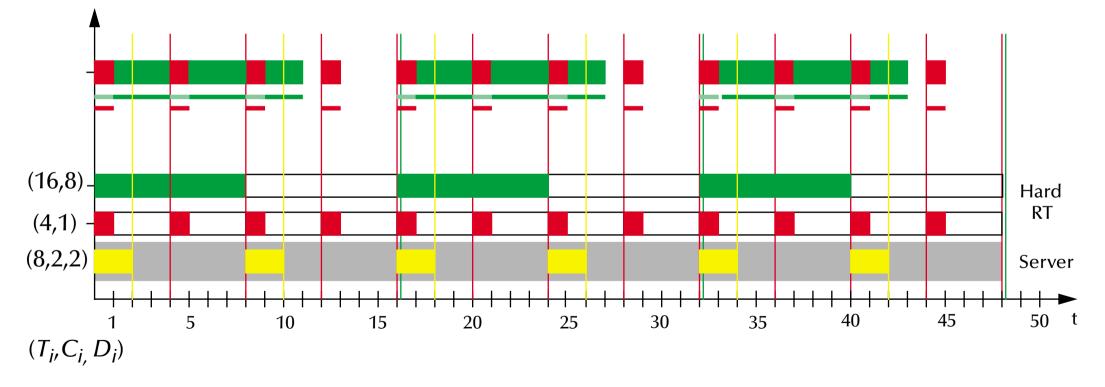

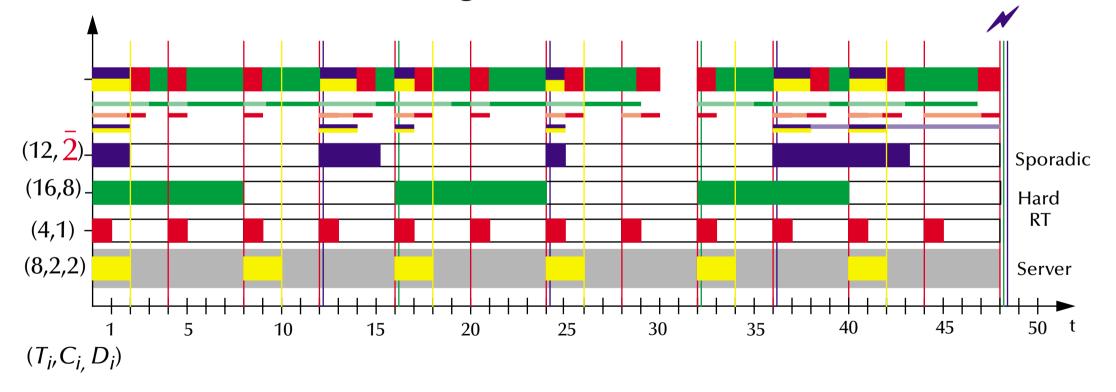

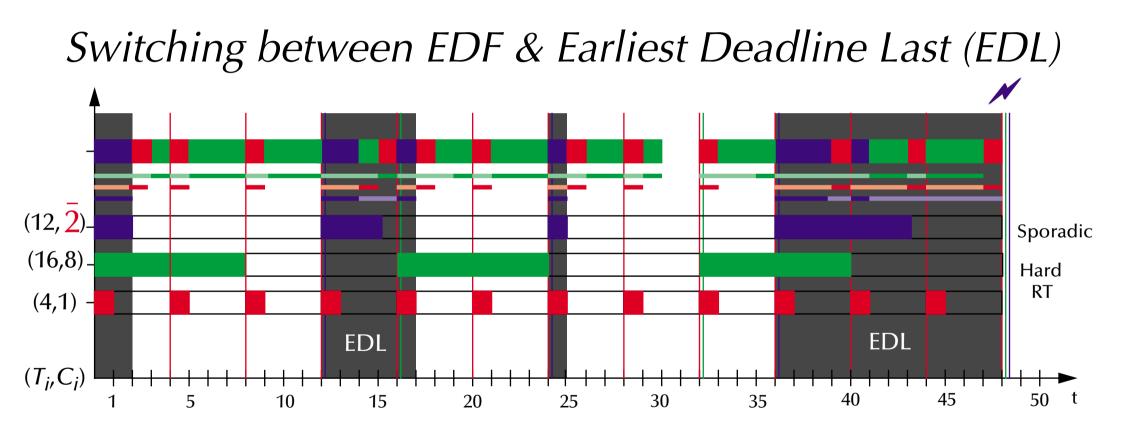

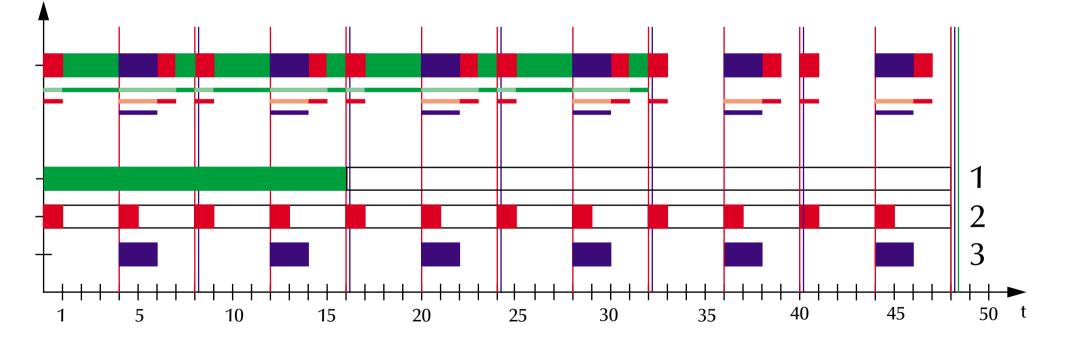

- Aperiodic, sporadic, and synchronized tasks

### Table of contents

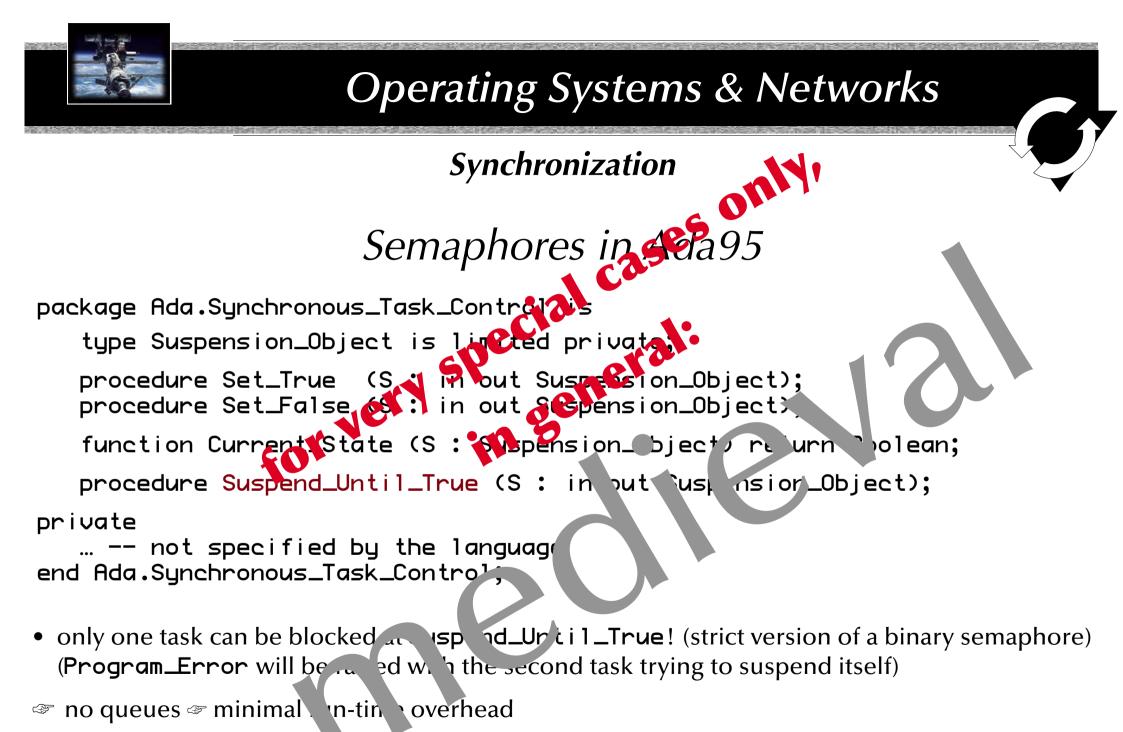

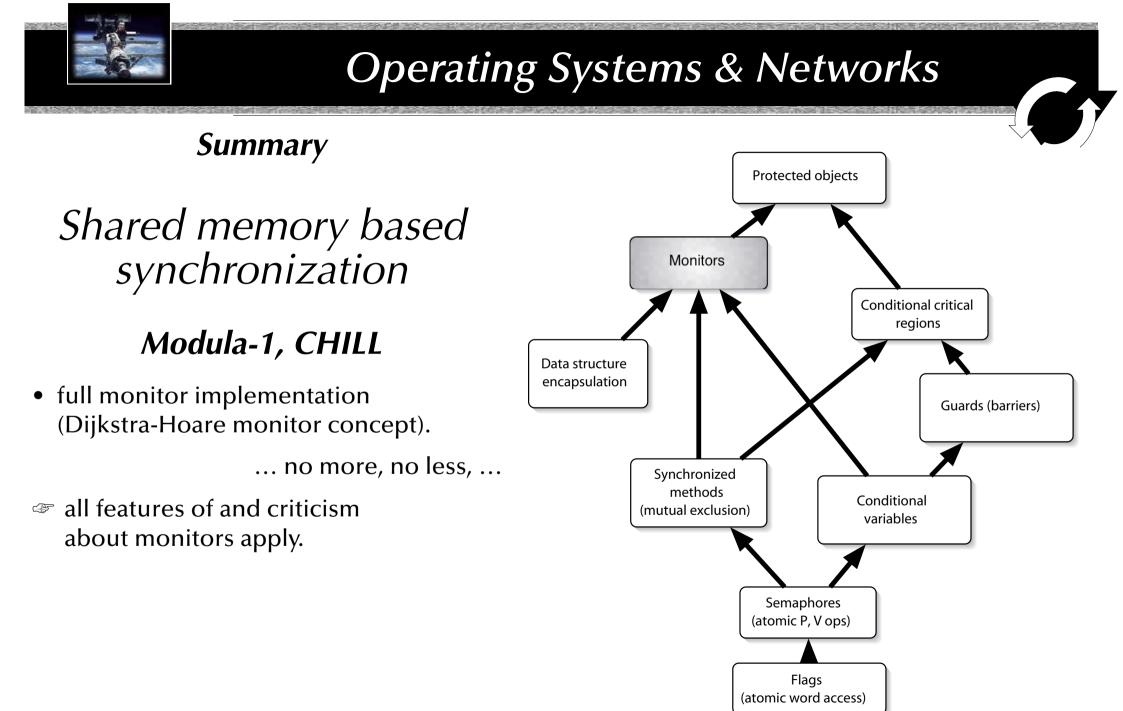

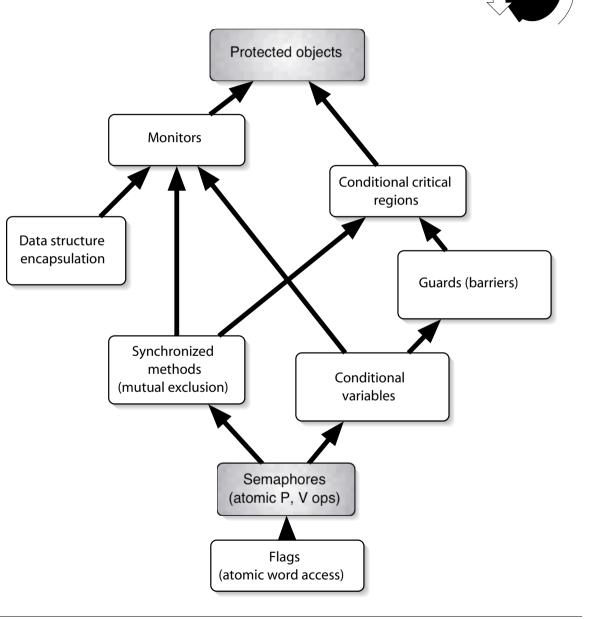

## 3.1 Synchronization methods

#### • Shared memory based synchronization

- Semaphores

- Conditional critical regions

- Monitors

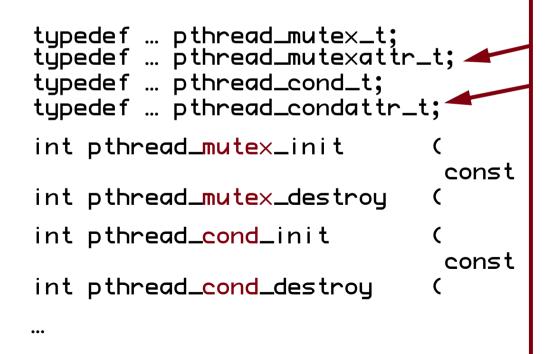

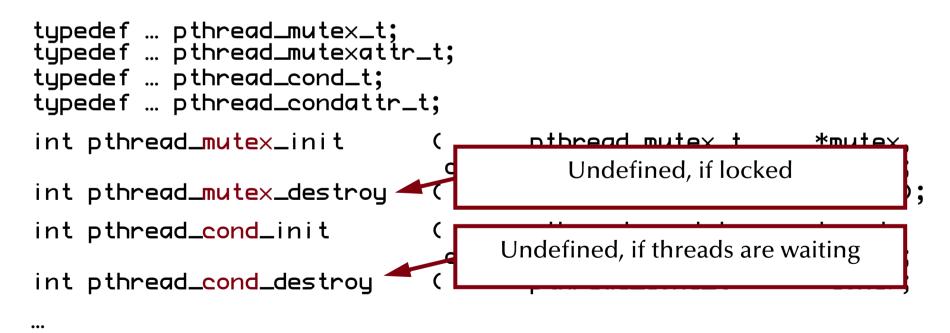

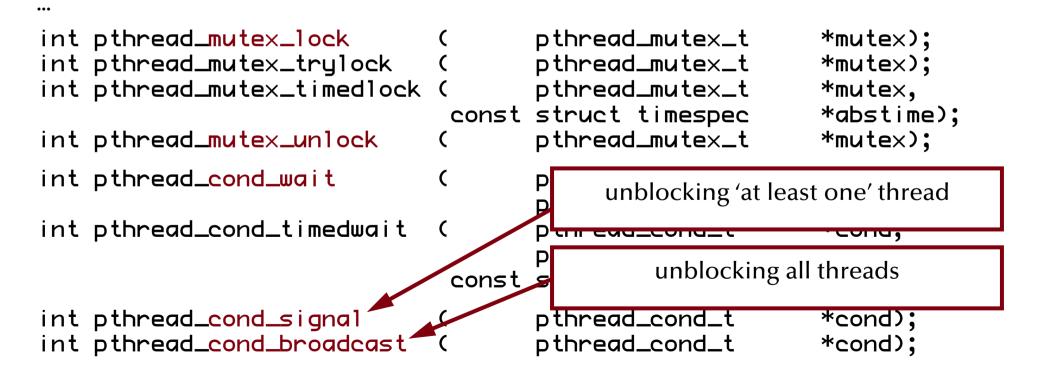

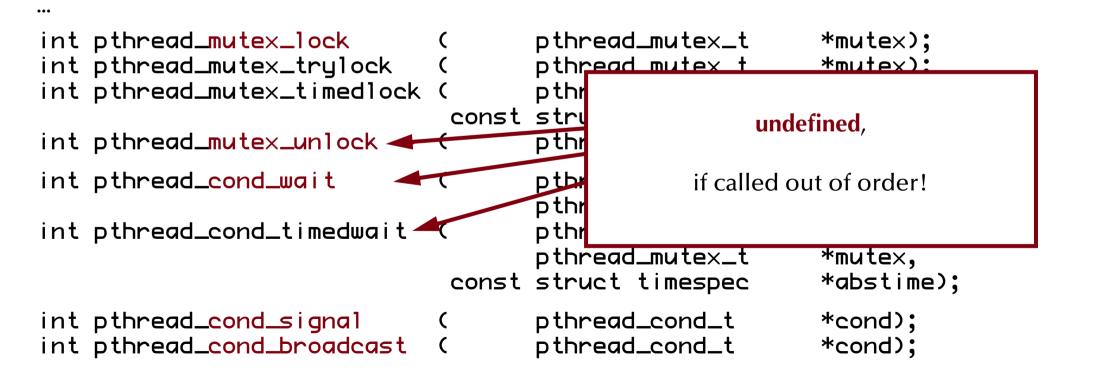

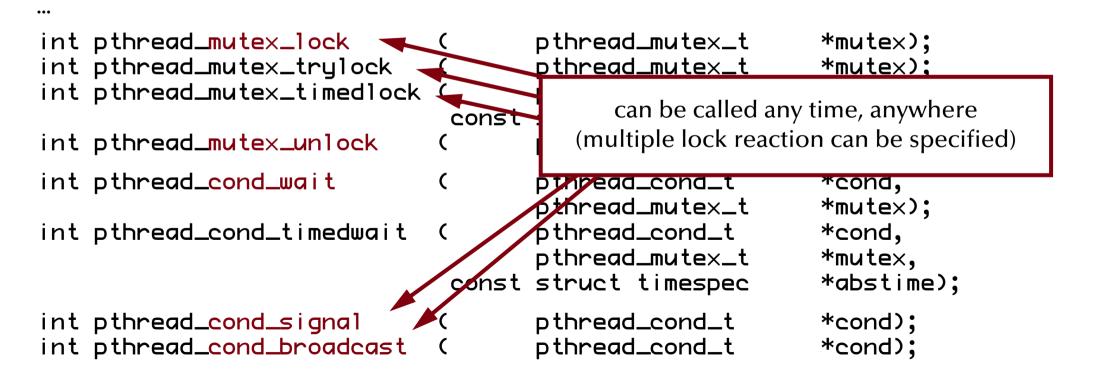

- Mutexes & conditional variables

- Synchronized methods

- Protected objects

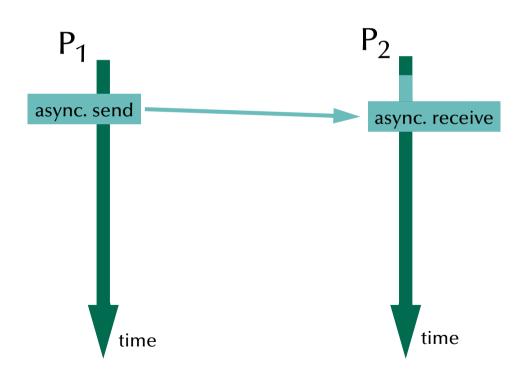

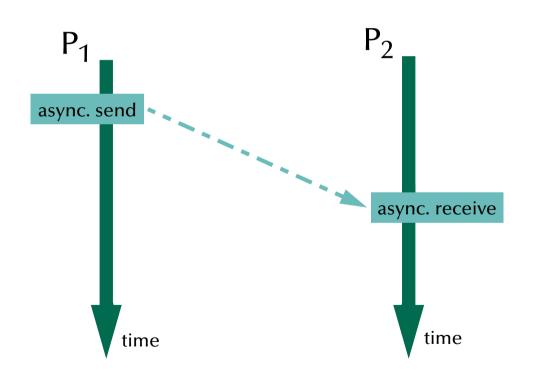

#### • Message based synchronization

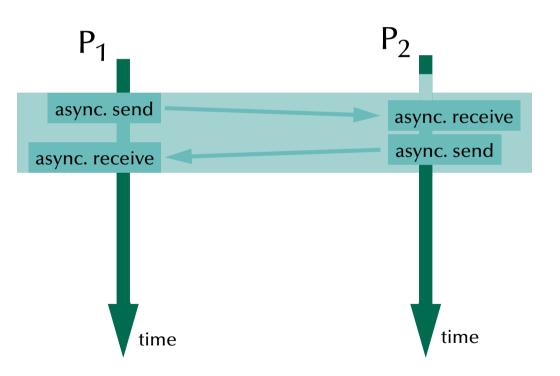

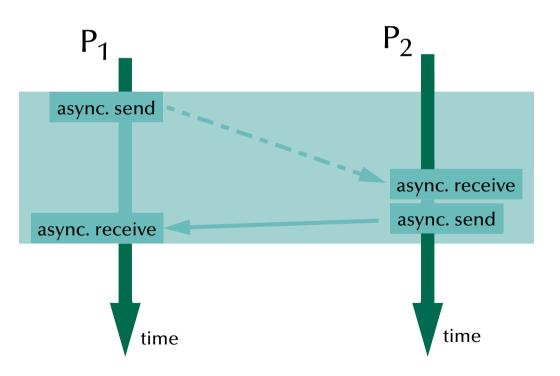

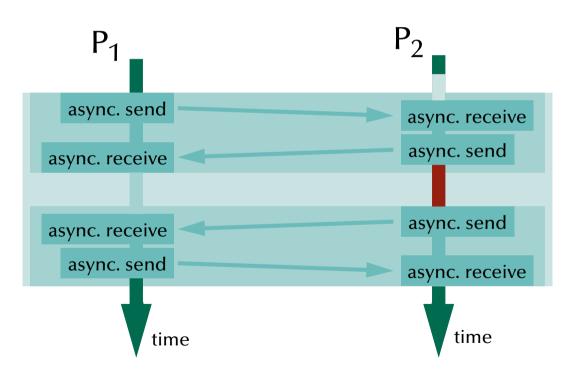

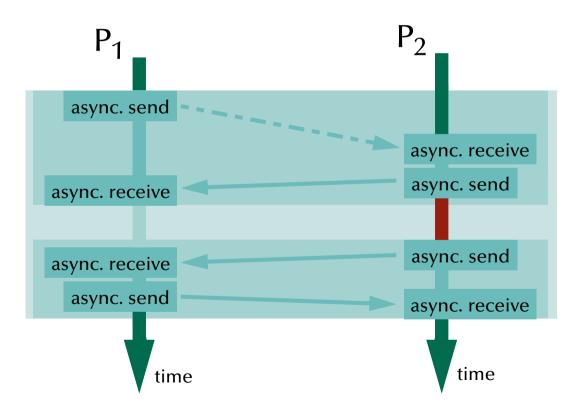

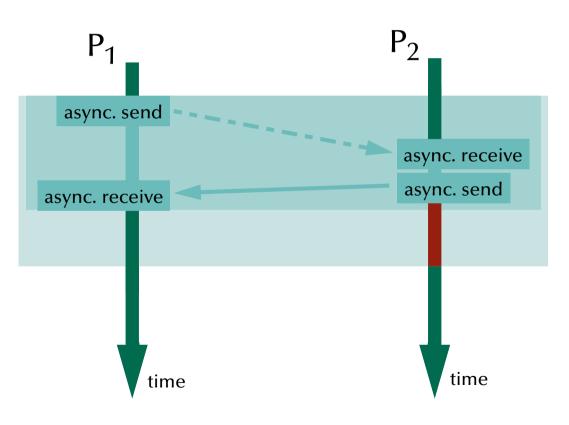

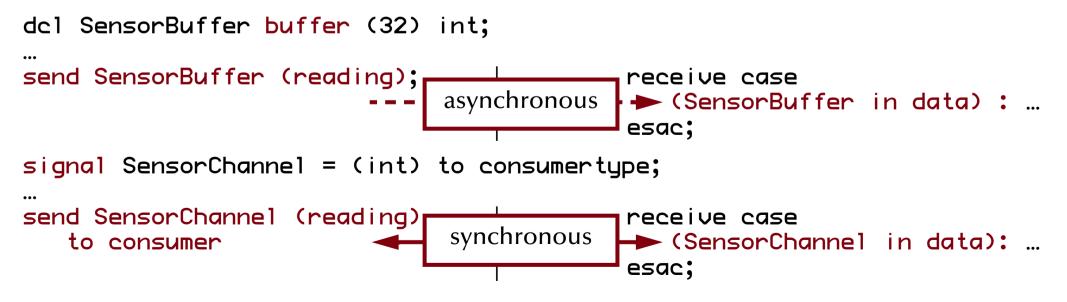

- Asynchronous messages

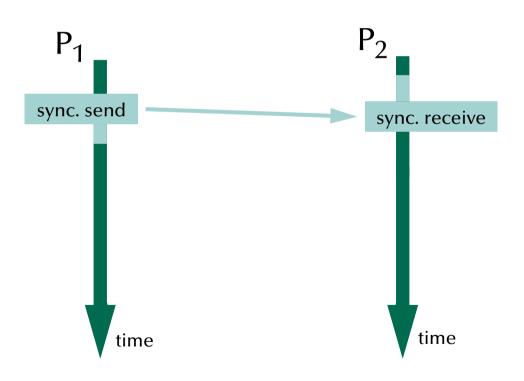

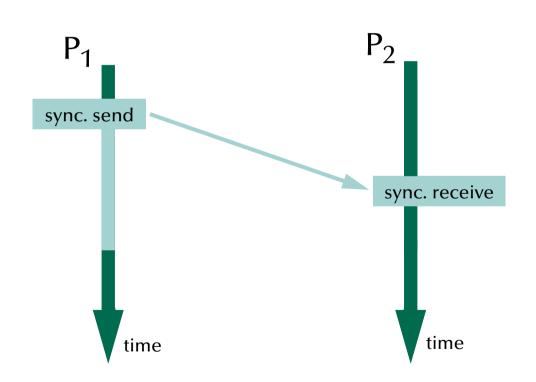

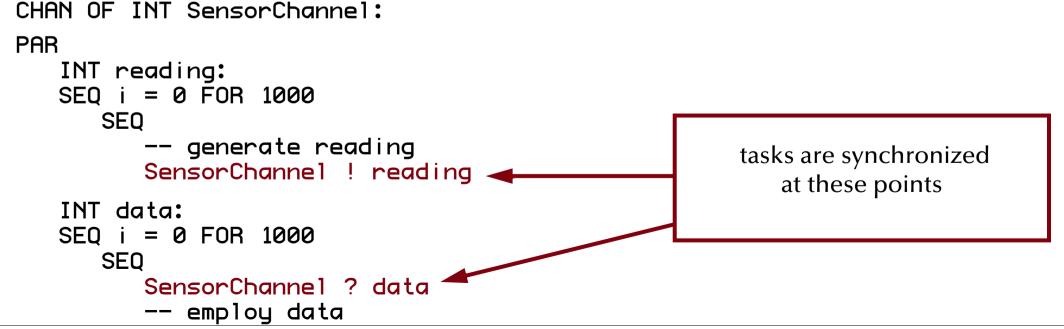

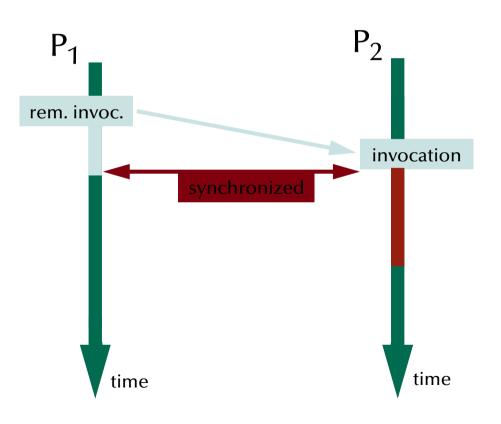

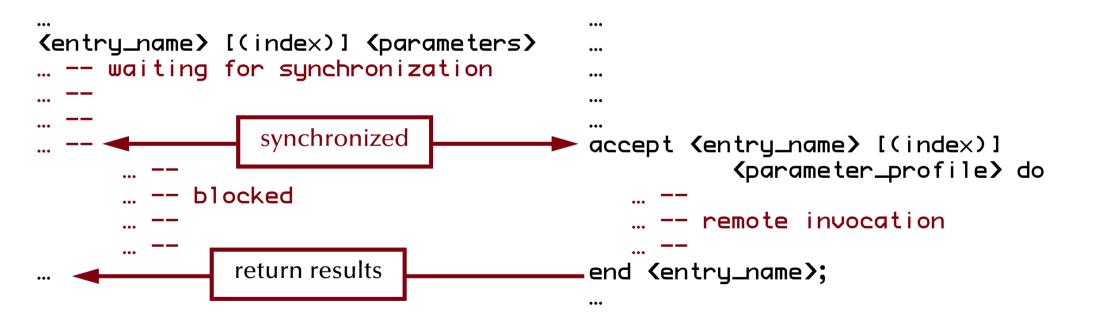

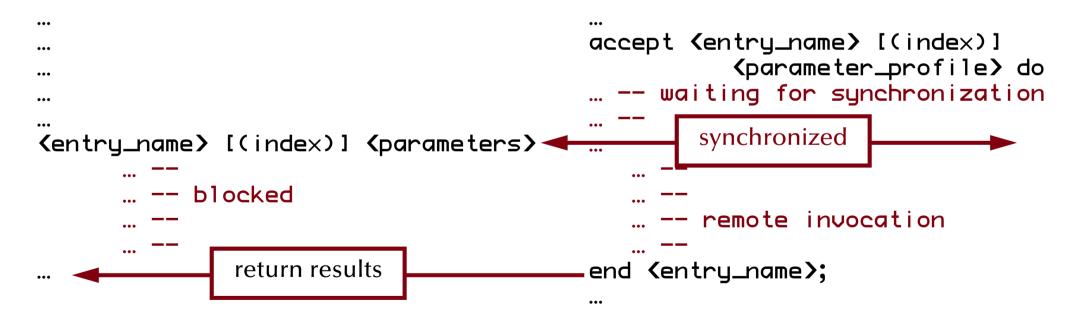

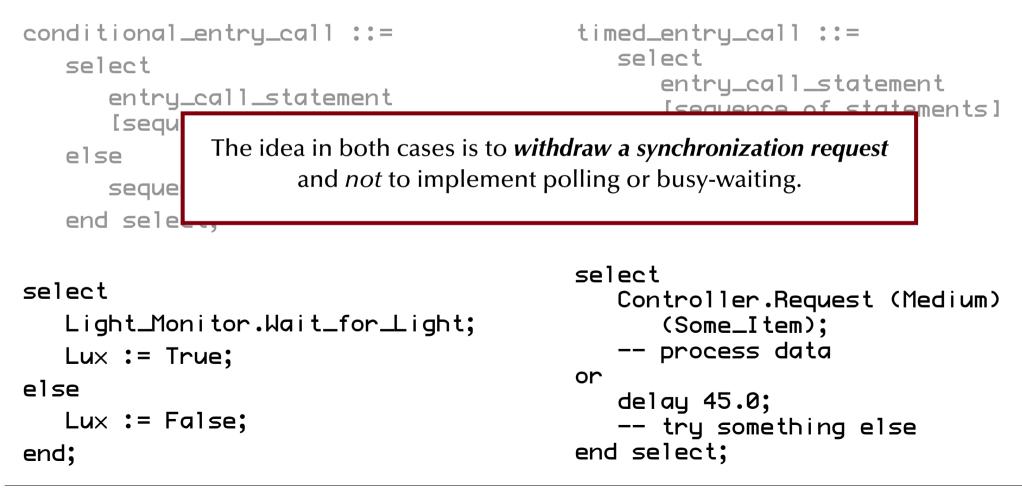

- Synchronous messages

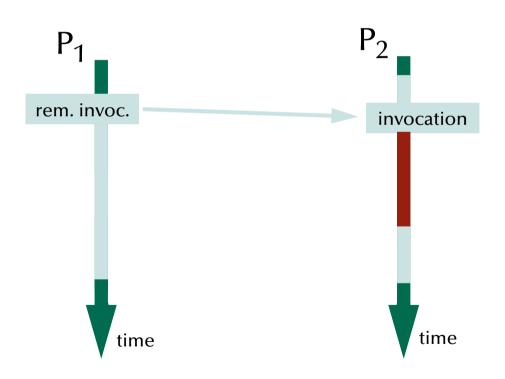

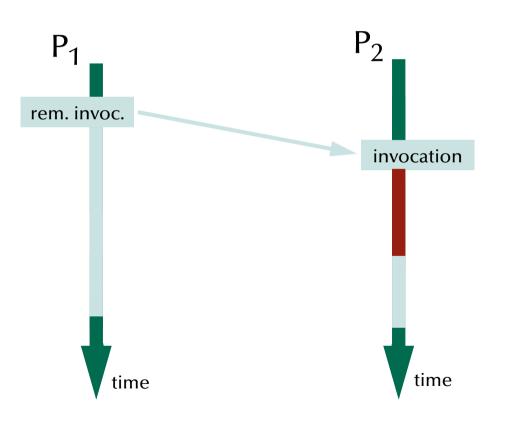

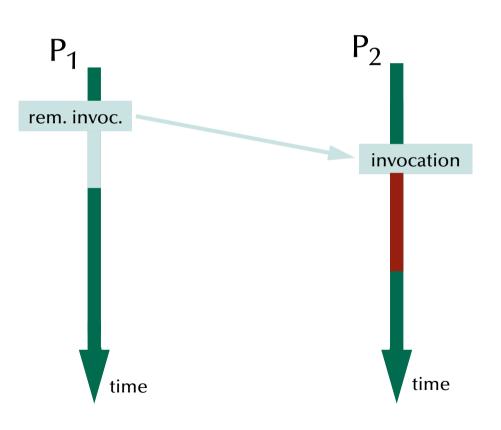

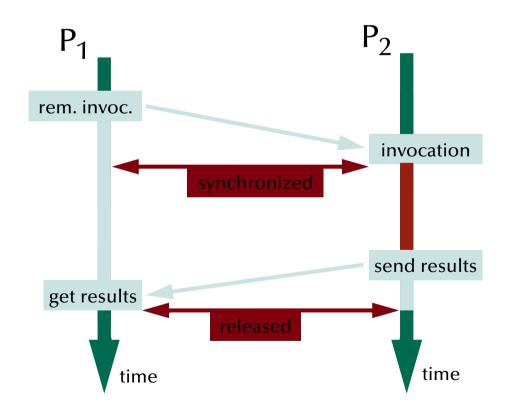

- Remote invocation, remote procedure call

- Synchronization in distributed systems

- ☞ 'C', POSIX Dijkstra

- Edison (experimental)

- Modula-1, Mesa Dijkstra, Hoare, ...

- POSIX ®

- Real-time Java

- ☞ Ada95

### Table of contents

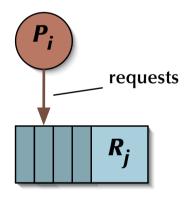

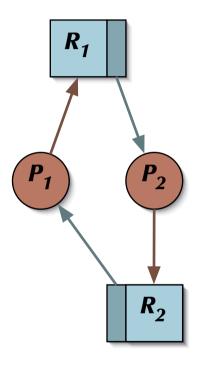

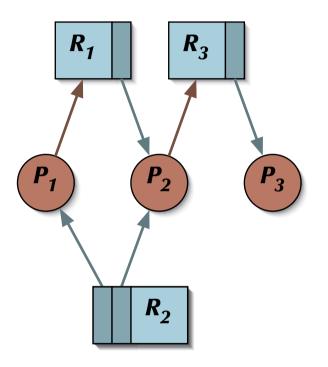

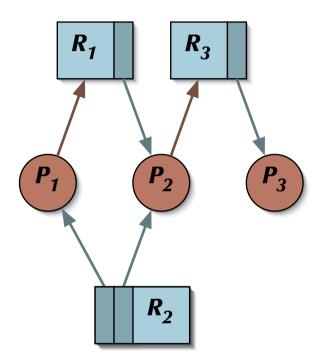

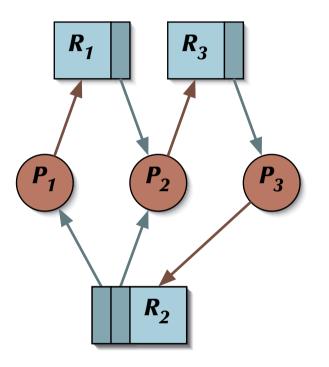

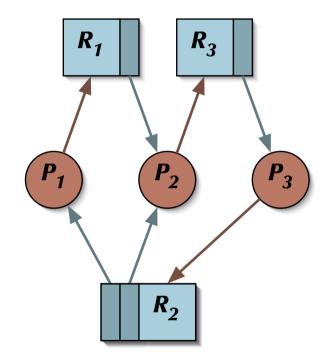

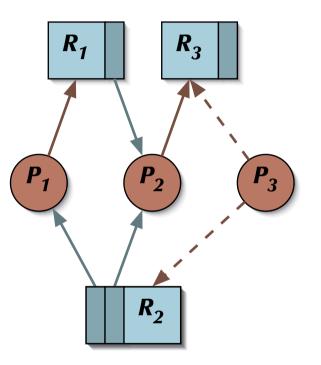

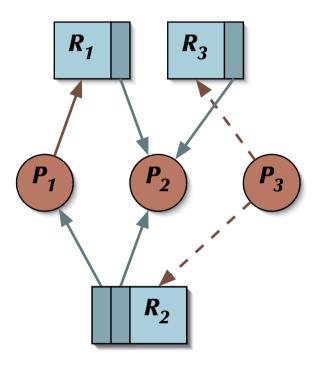

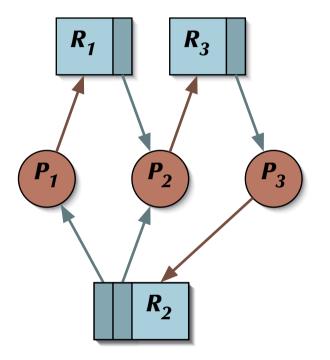

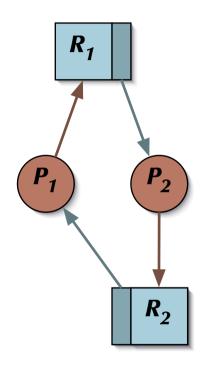

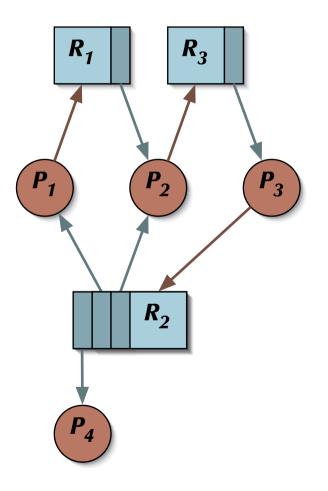

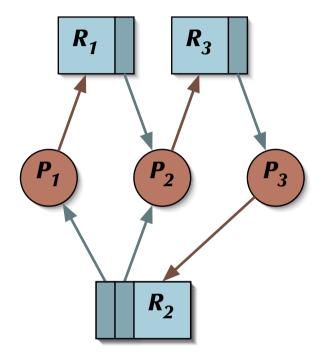

# 3.2 Deadlocks

#### • Ignorance & recovery

• *(approx 'kill some seemingly persistently blocked processes from time to time' (exasperation)*

#### • Deadlock detection & recovery

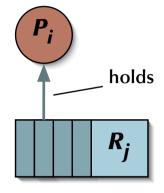

- The multiple methods for detection, e.g. resource allocation graphs, Banker's algorithm

- recovery is mostly 'ugly'

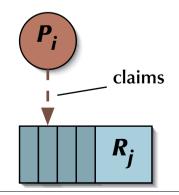

#### • Deadlock avoidance

• The check system safety before allocating resources, e.g. Banker's algorithm

#### • Deadlock prevention

• *are eliminate one of the pre-conditions for deadlocks*

### Table of contents

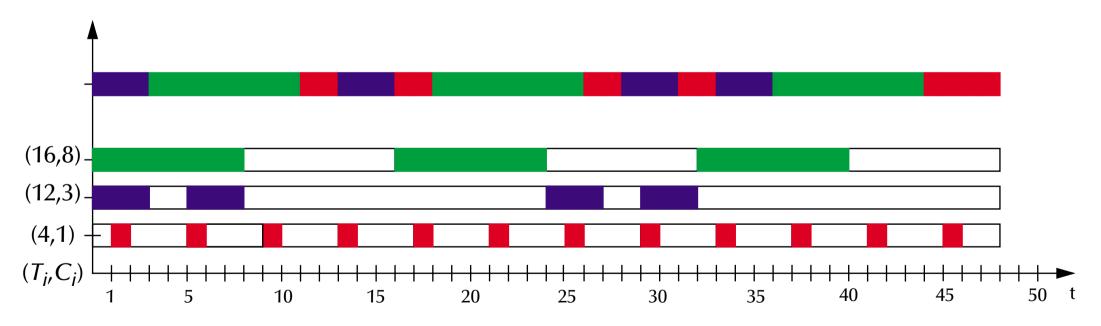

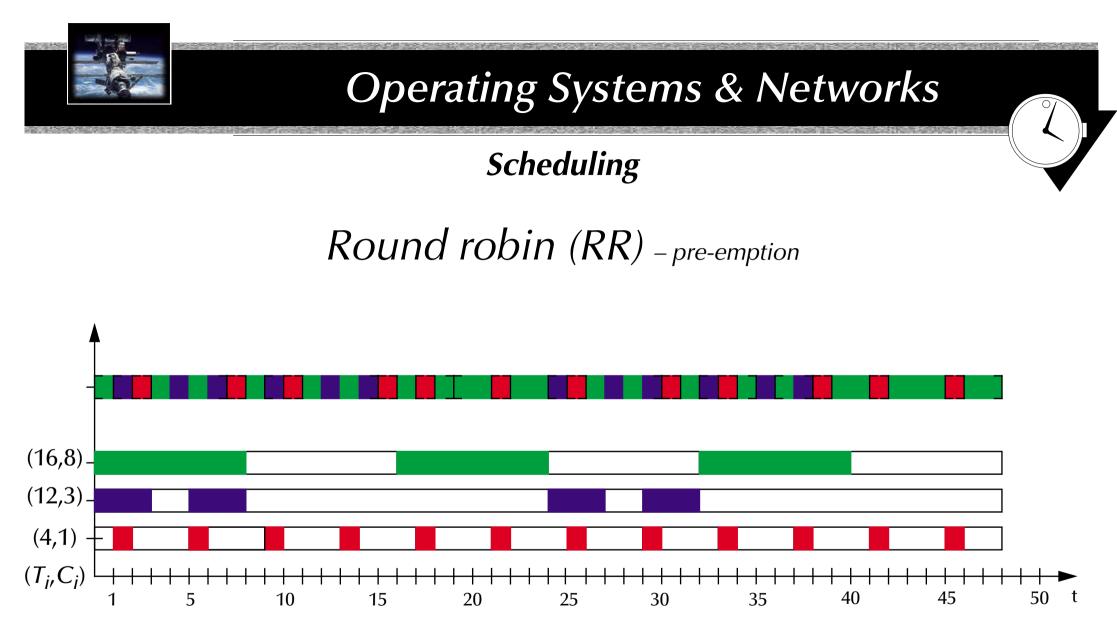

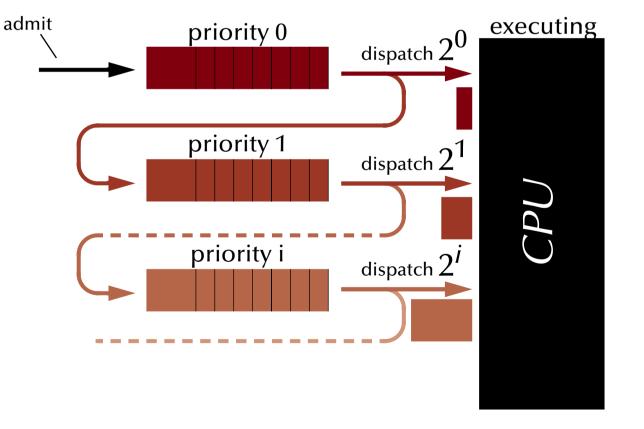

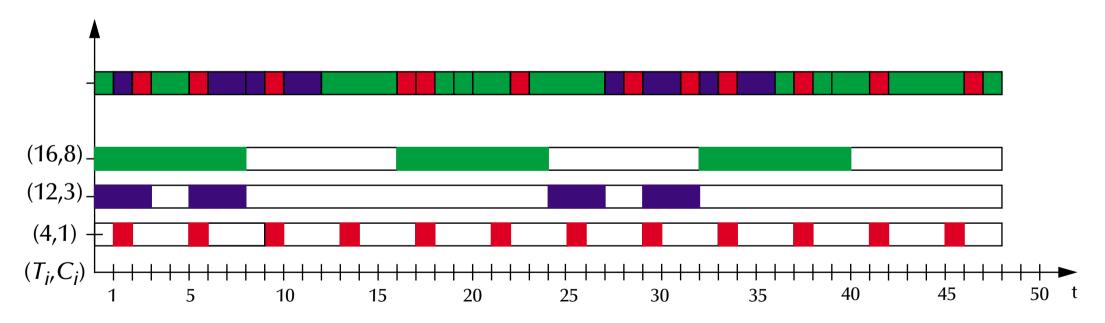

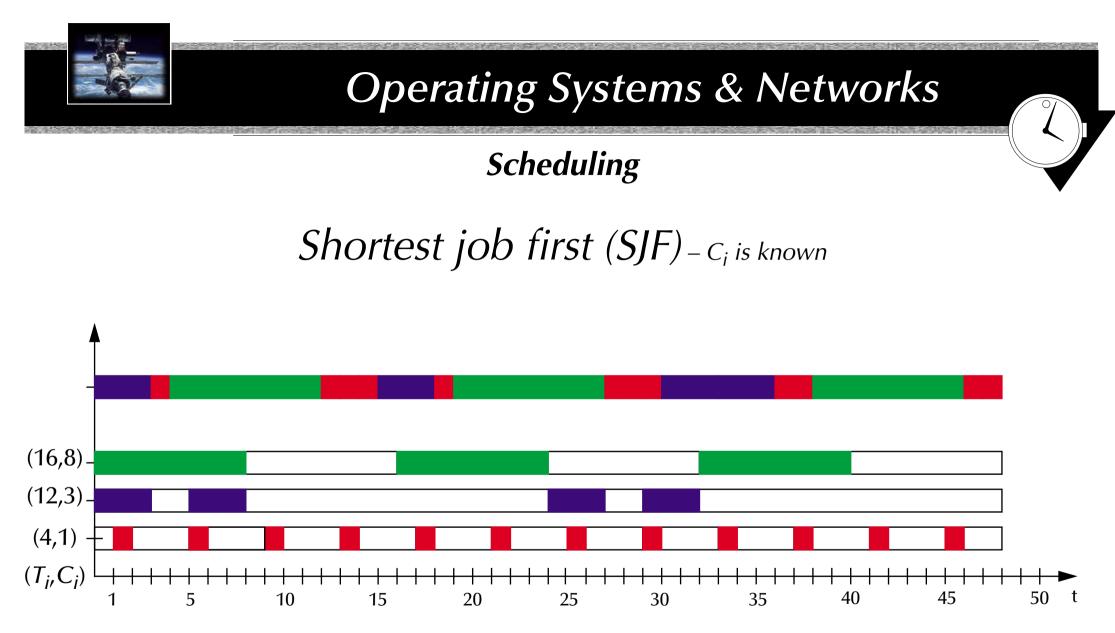

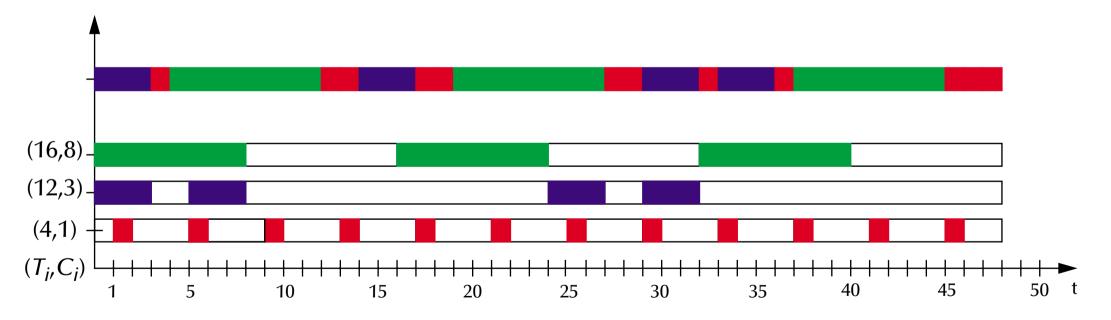

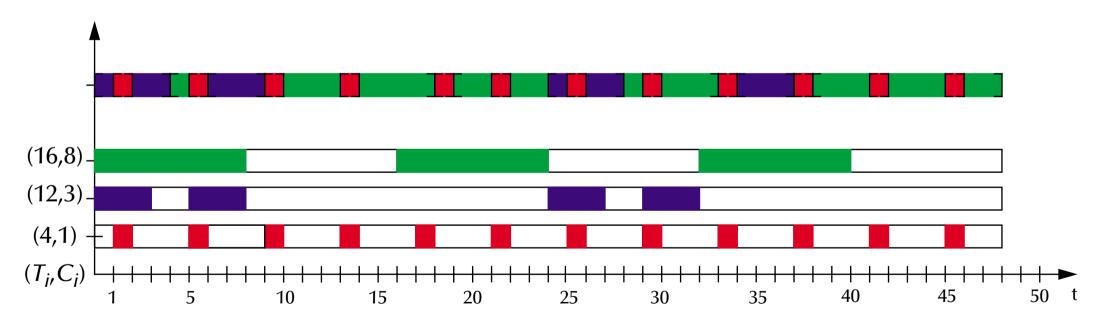

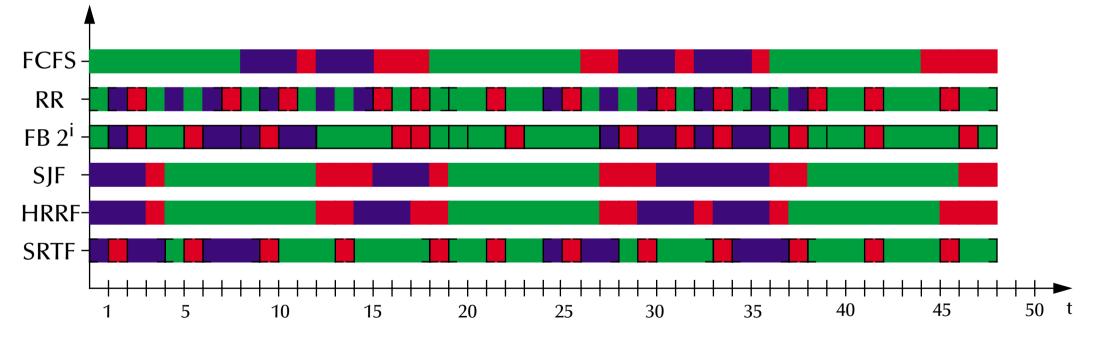

# 3.3 Scheduling

#### • Basic performance based scheduling

- *C<sub>i</sub> is not known*: first-come-first-served (FCFS), round robin (RR), and feedback-scheduling

- C<sub>i</sub> is known: shortest job first (SJF), highest response ration first (HRRF), shortest remaining time first (SRTF)-scheduling

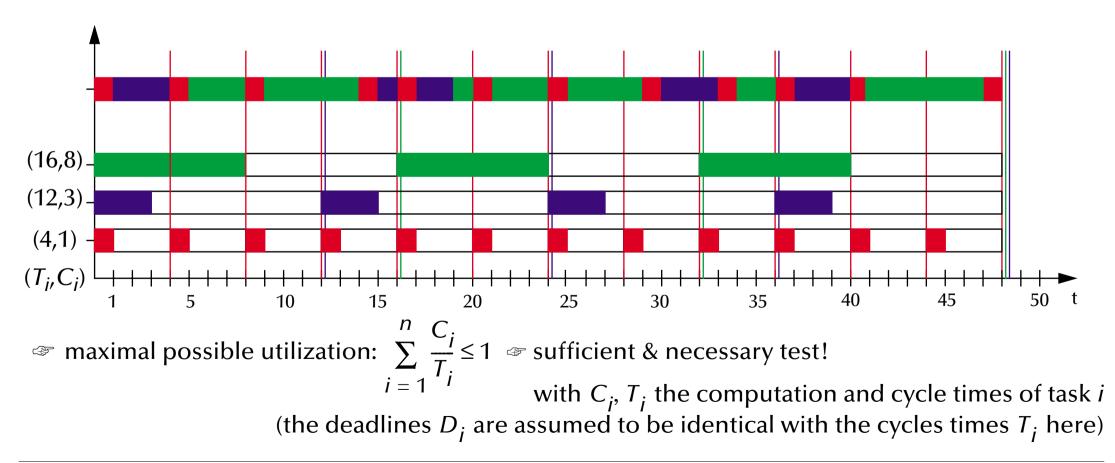

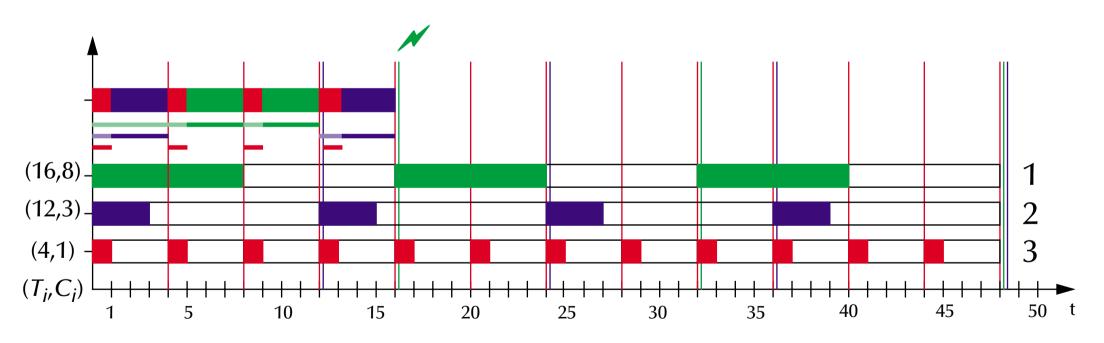

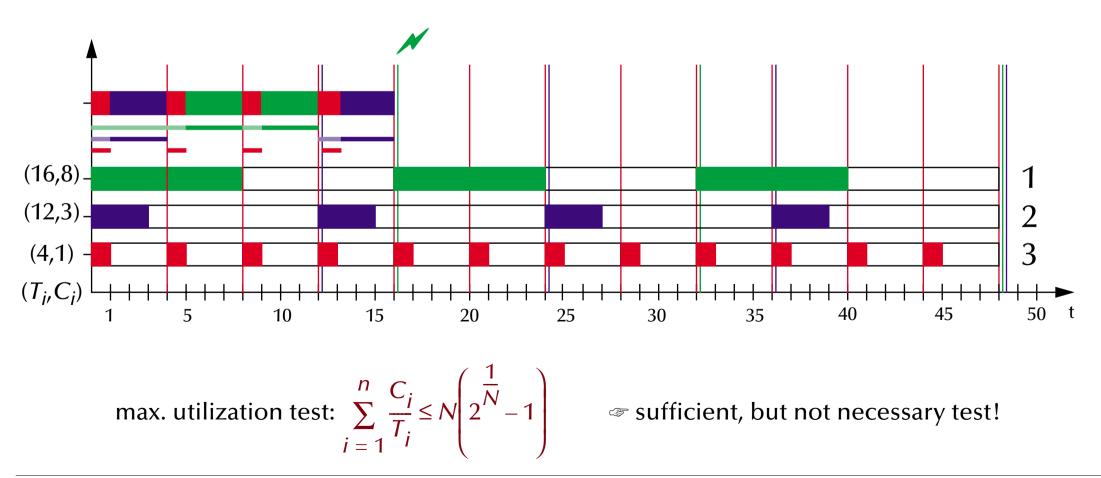

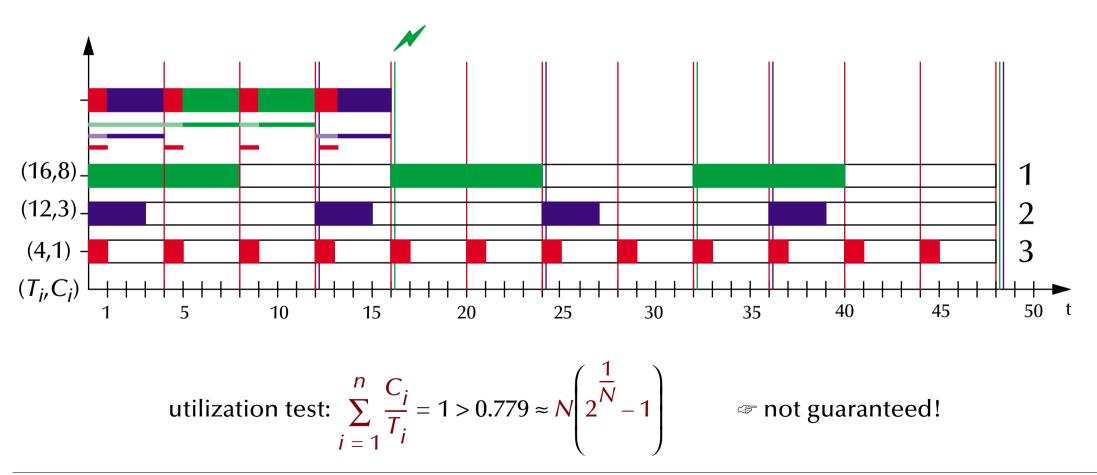

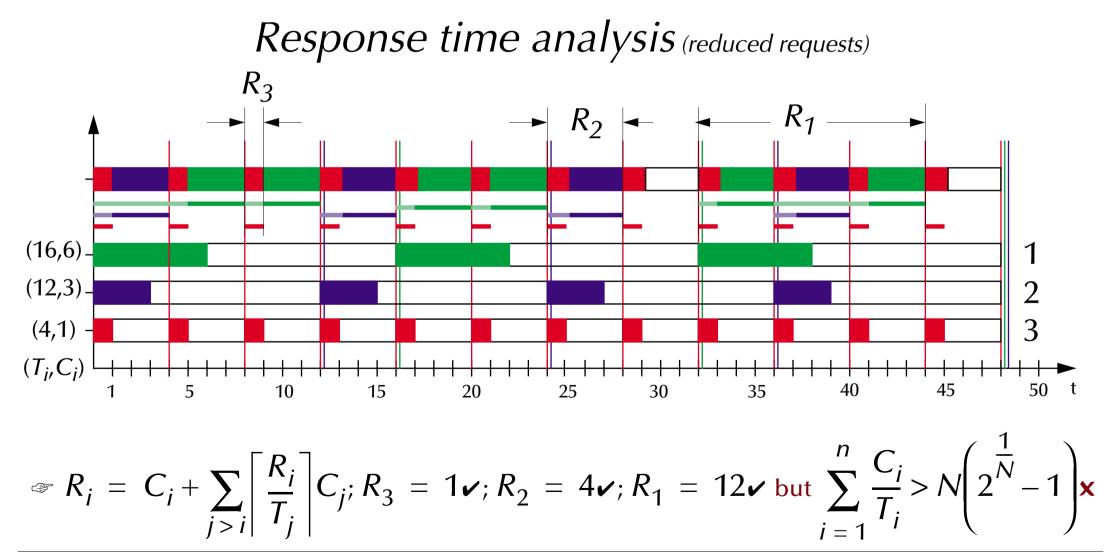

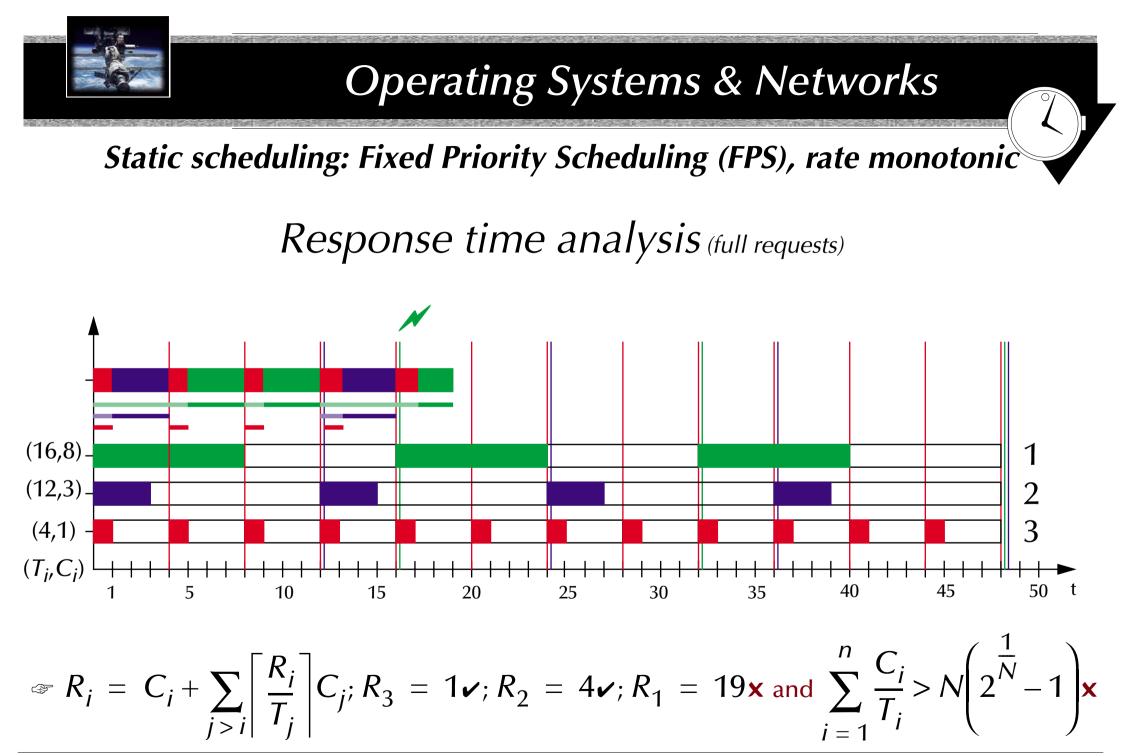

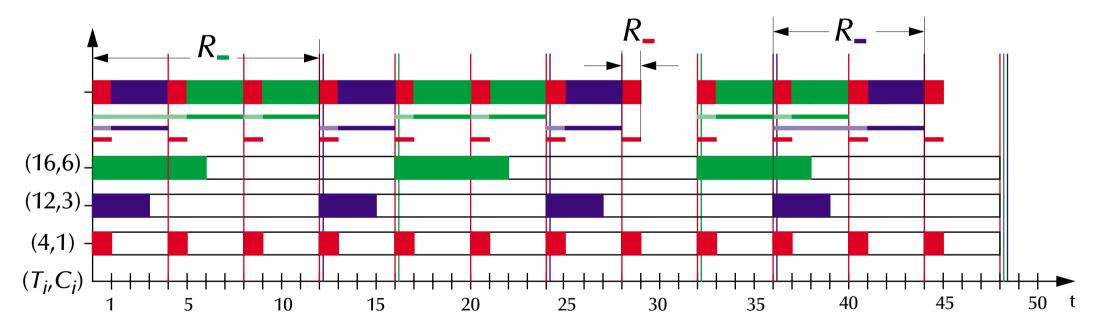

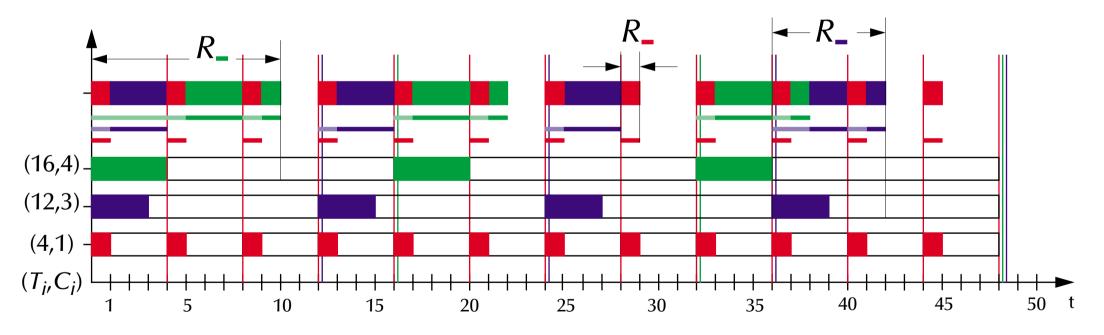

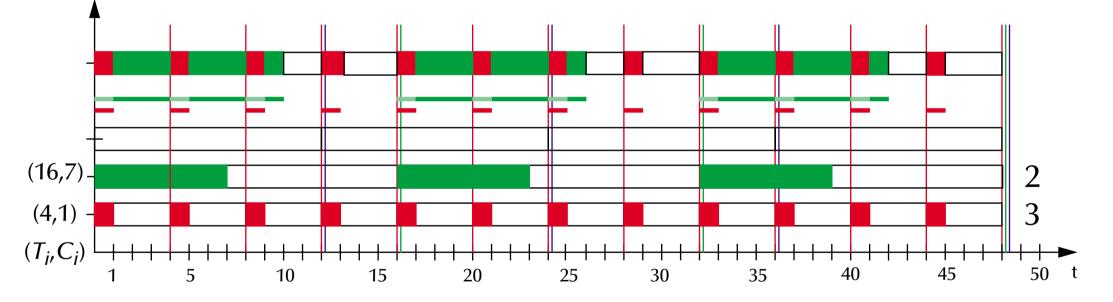

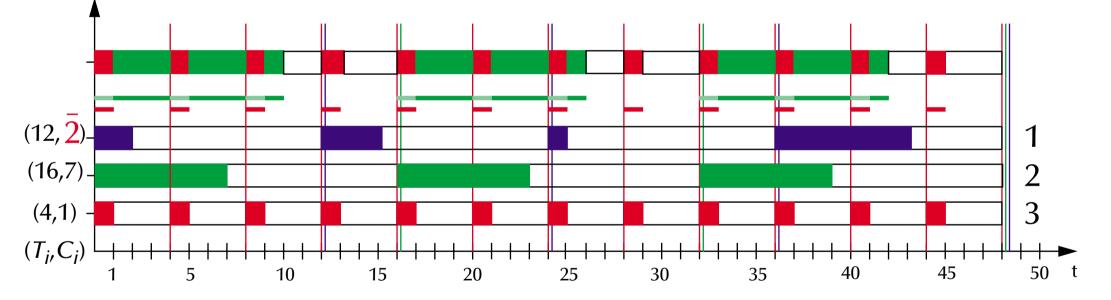

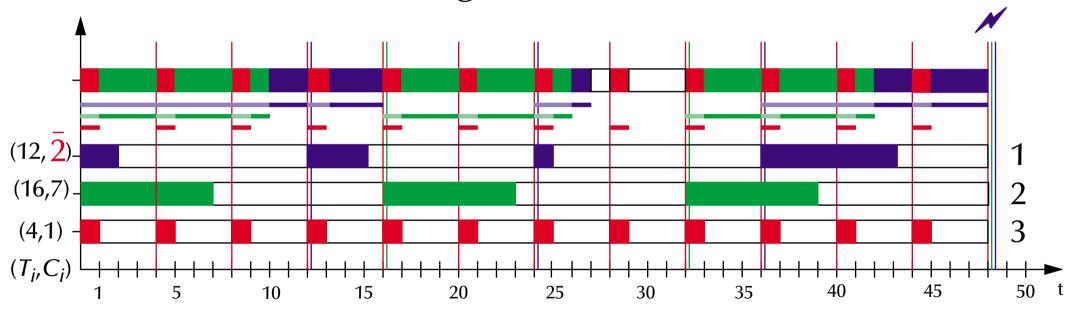

#### • Basic predictable scheduling

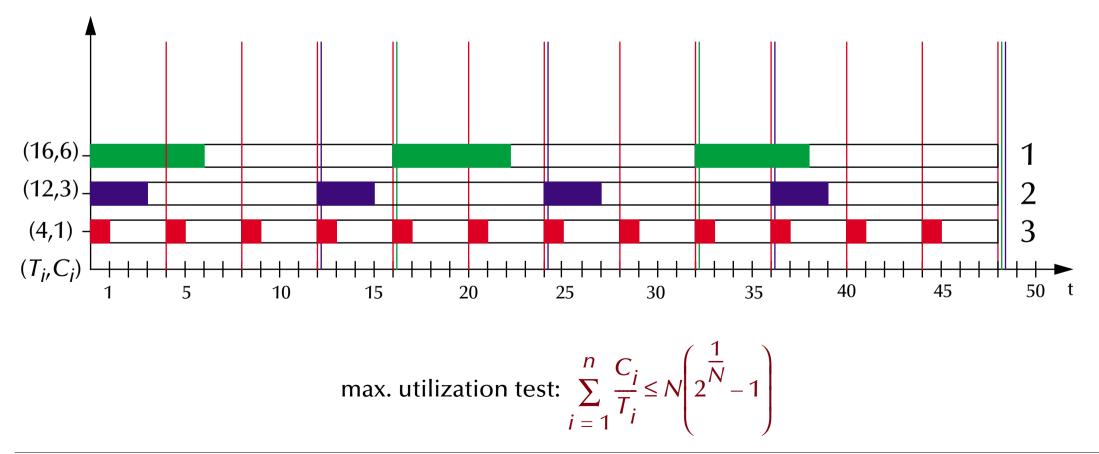

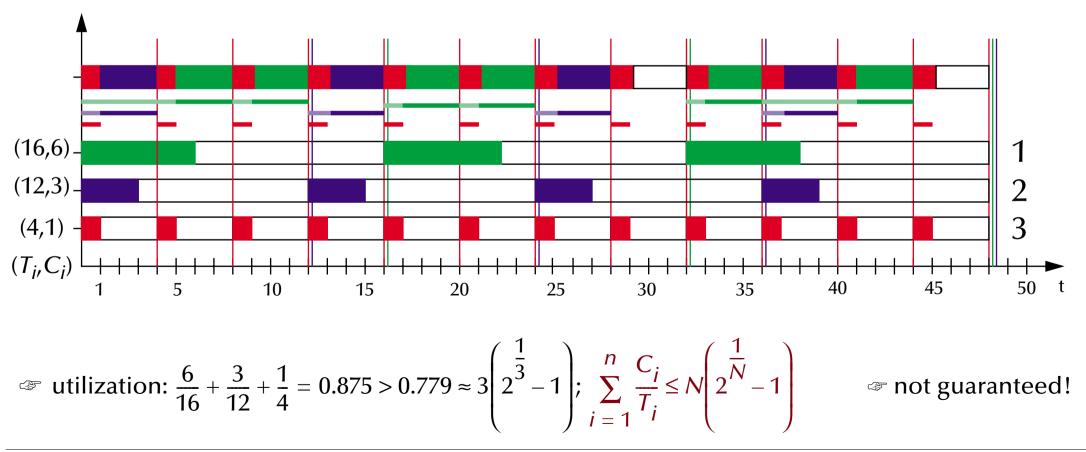

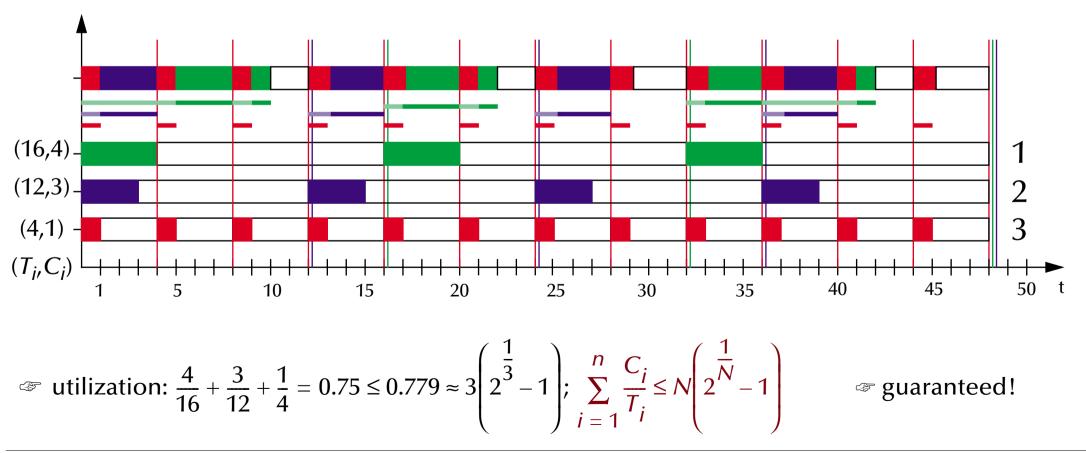

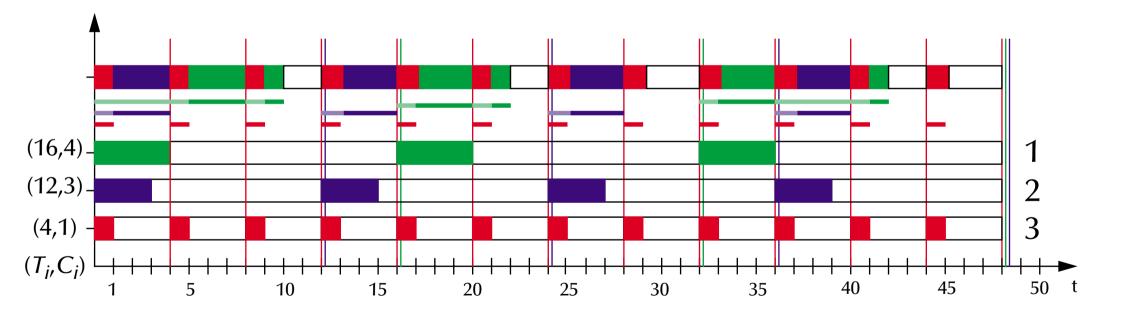

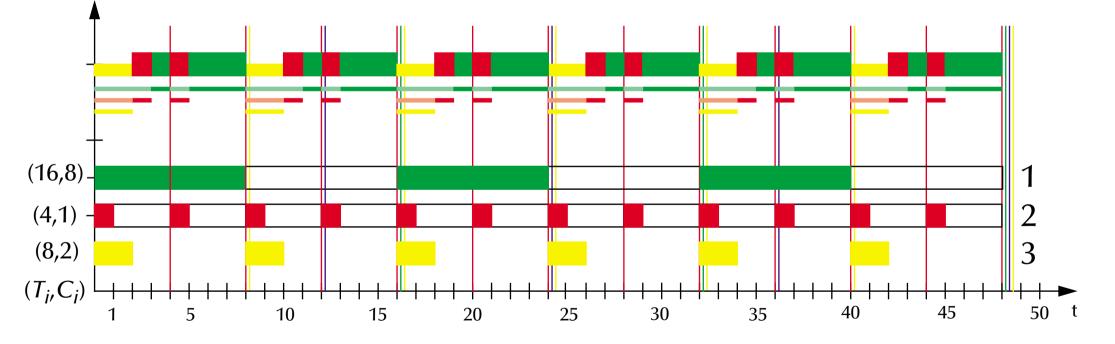

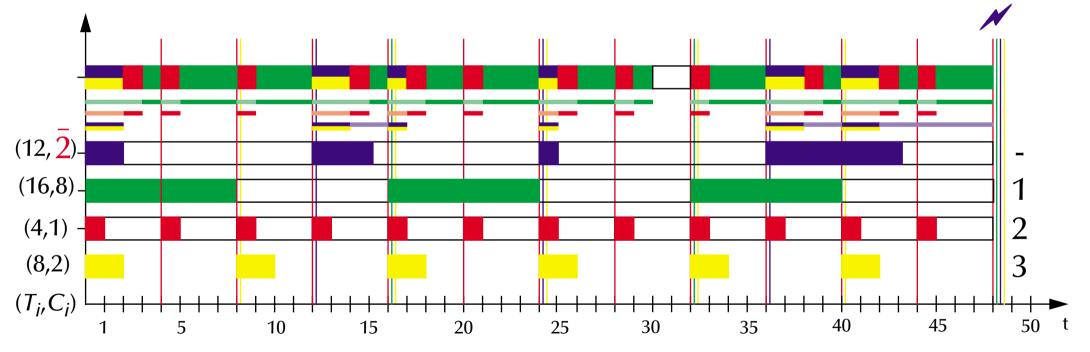

- Fixed Priority Scheduling (FPS) with Rate Monotonic (RMPO)

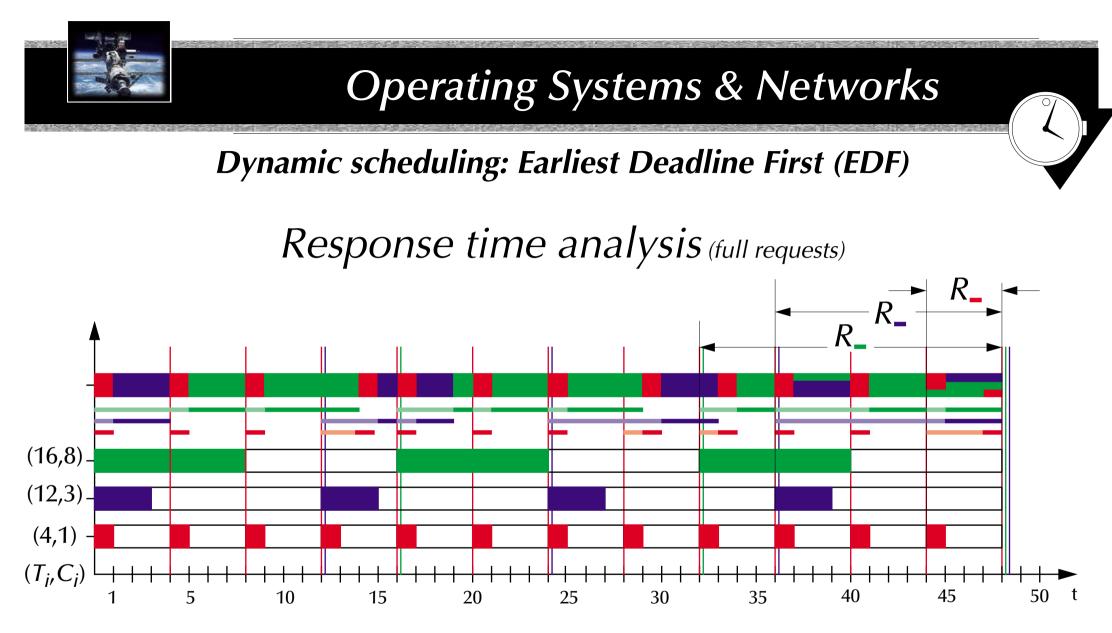

- Earliest Deadline First (EDF)

#### • Real-world extensions

- Aperiodic, sporadic, soft real-time tasks

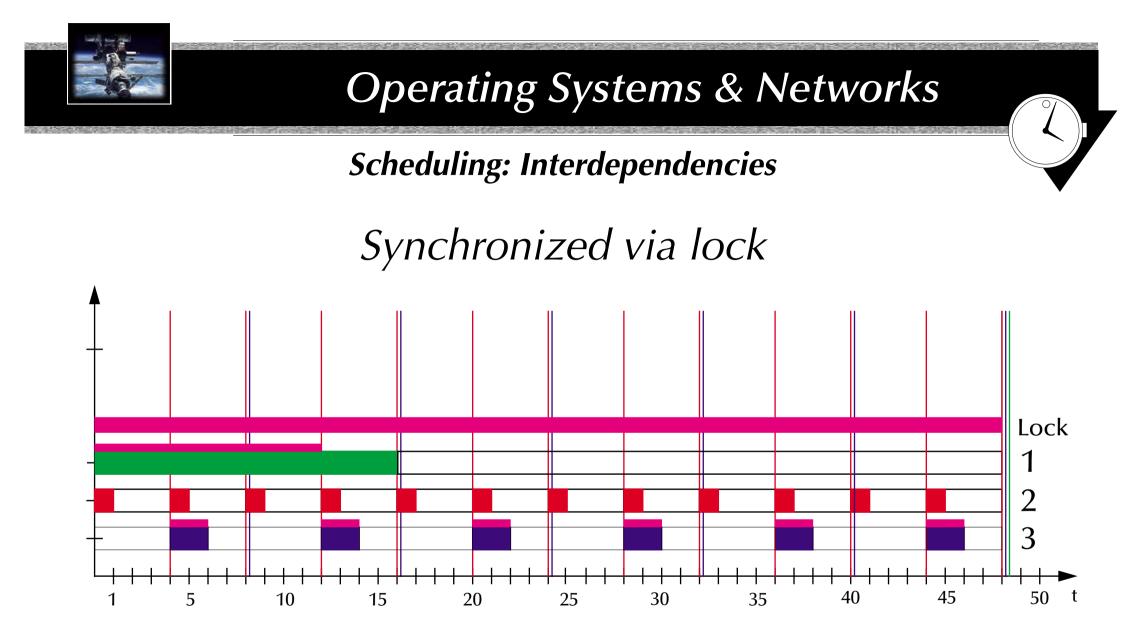

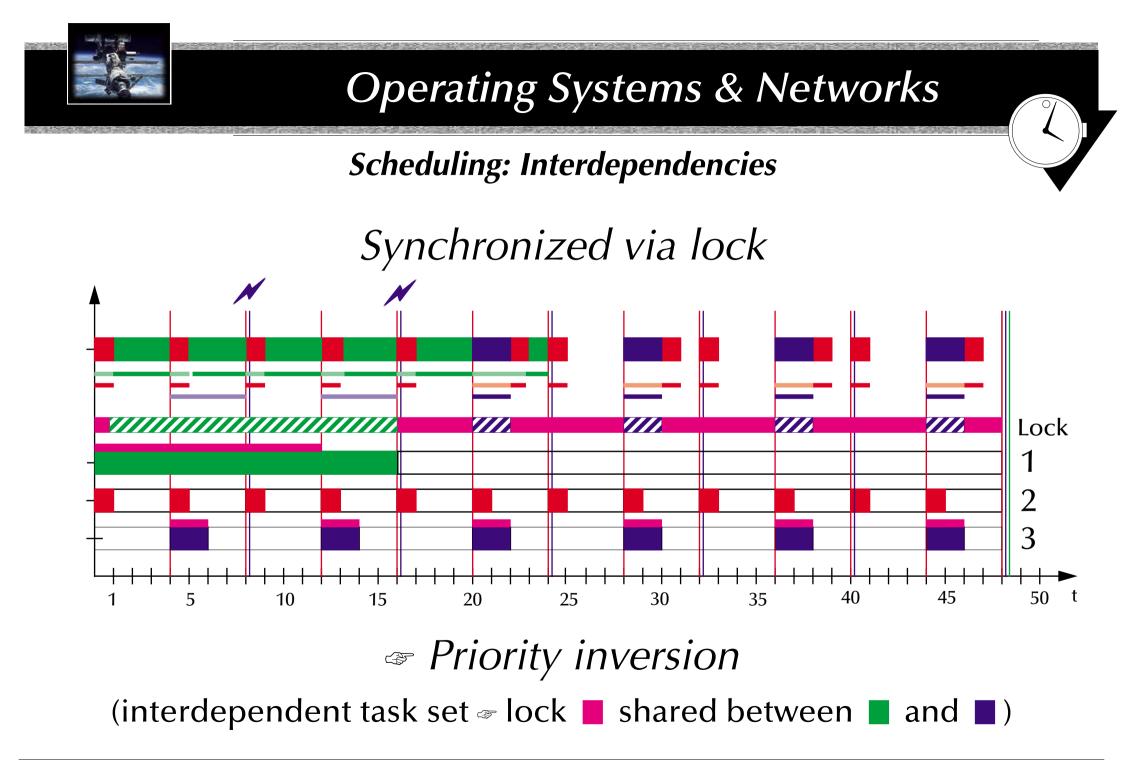

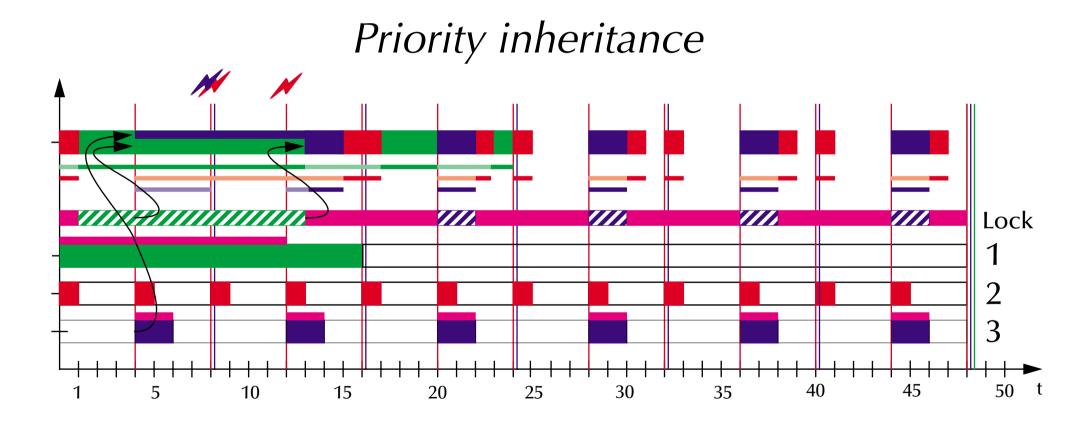

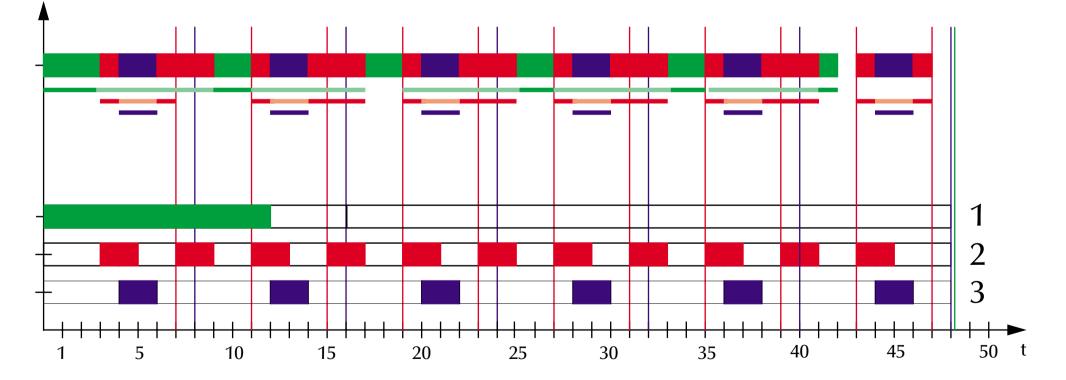

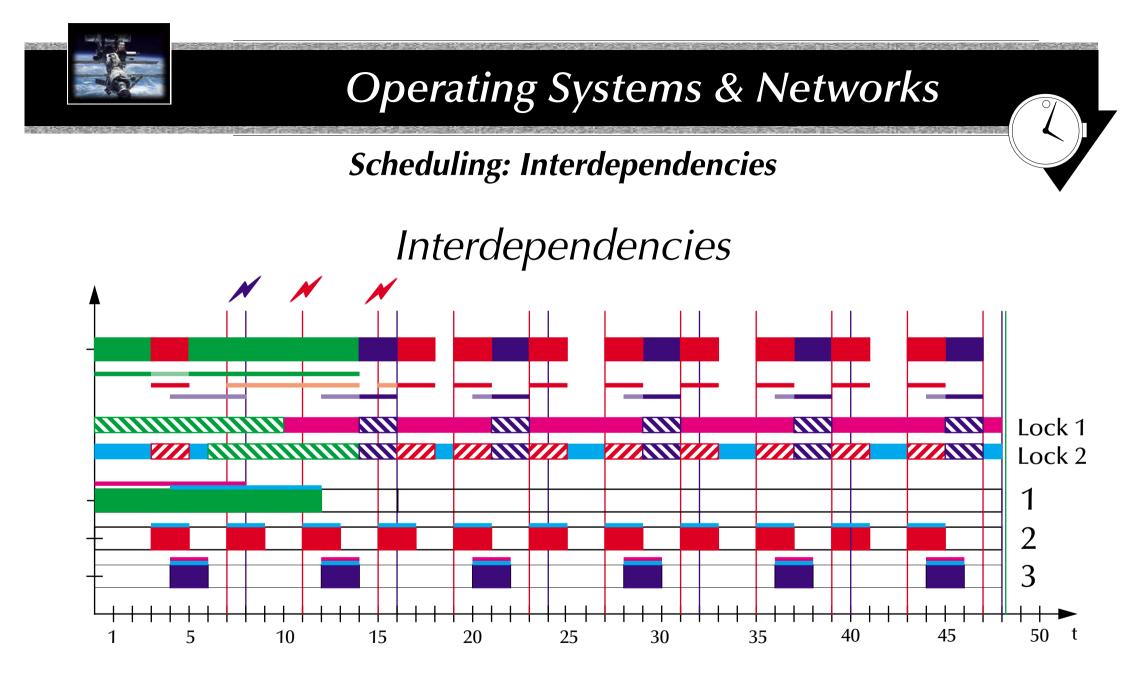

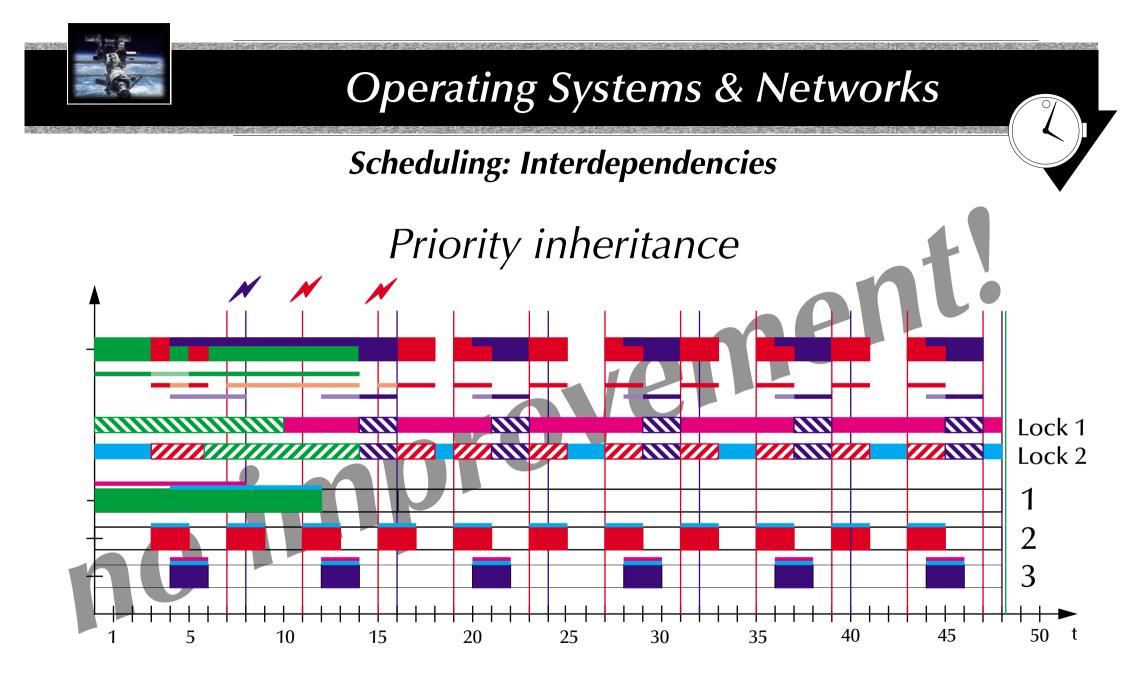

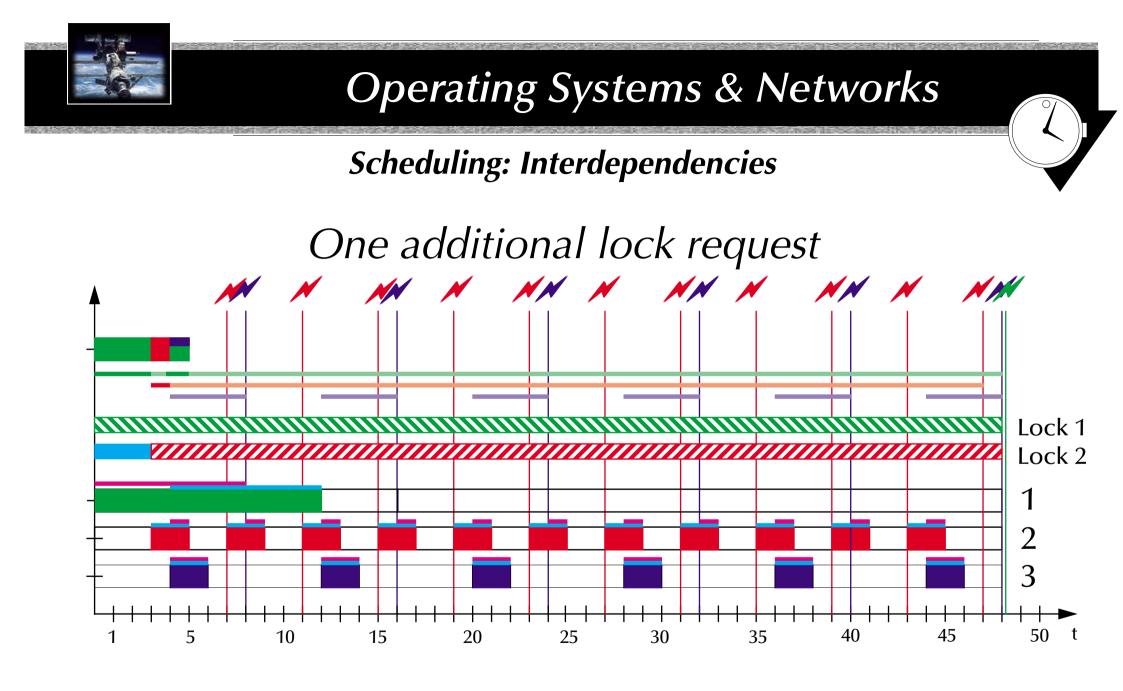

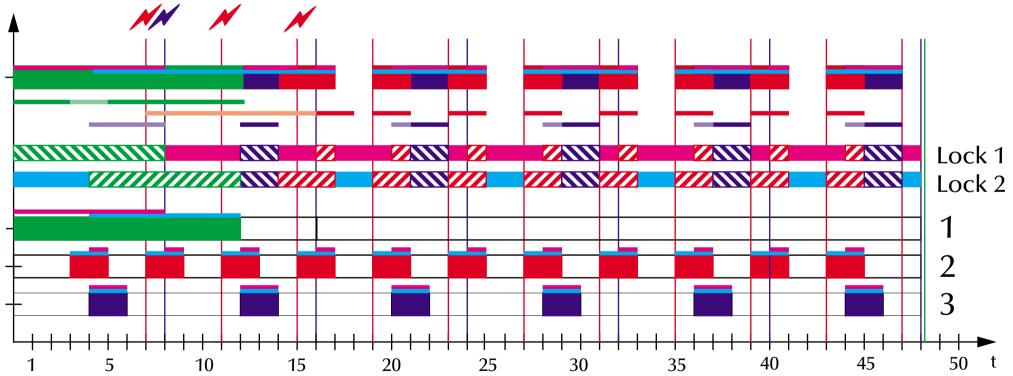

- Synchronized talks (priority inheritance, priority ceiling protocols)

#### Table of contents

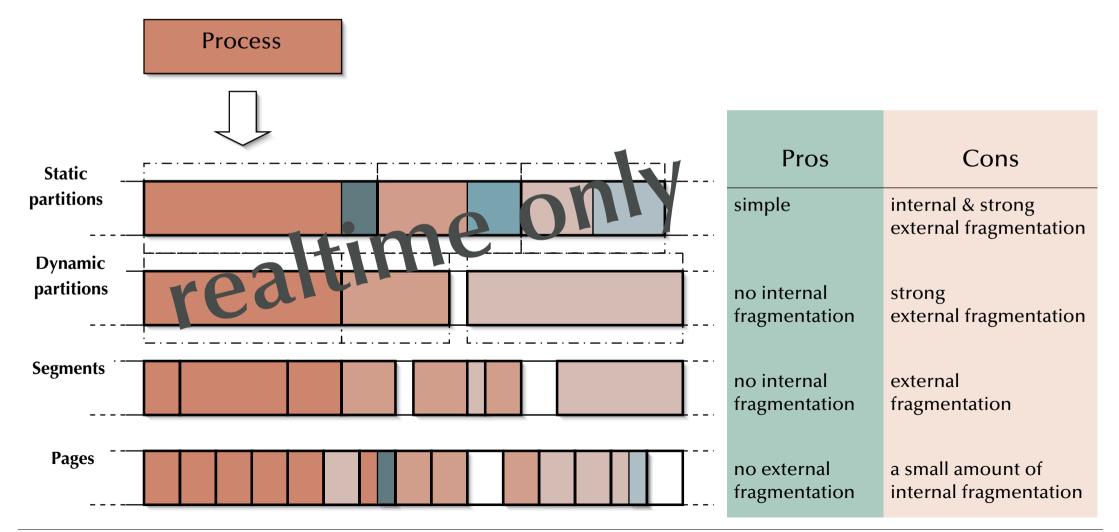

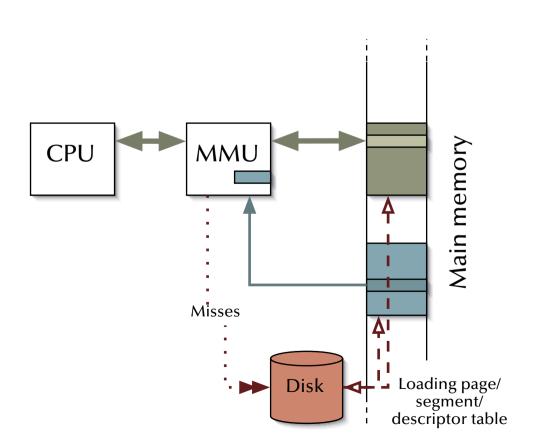

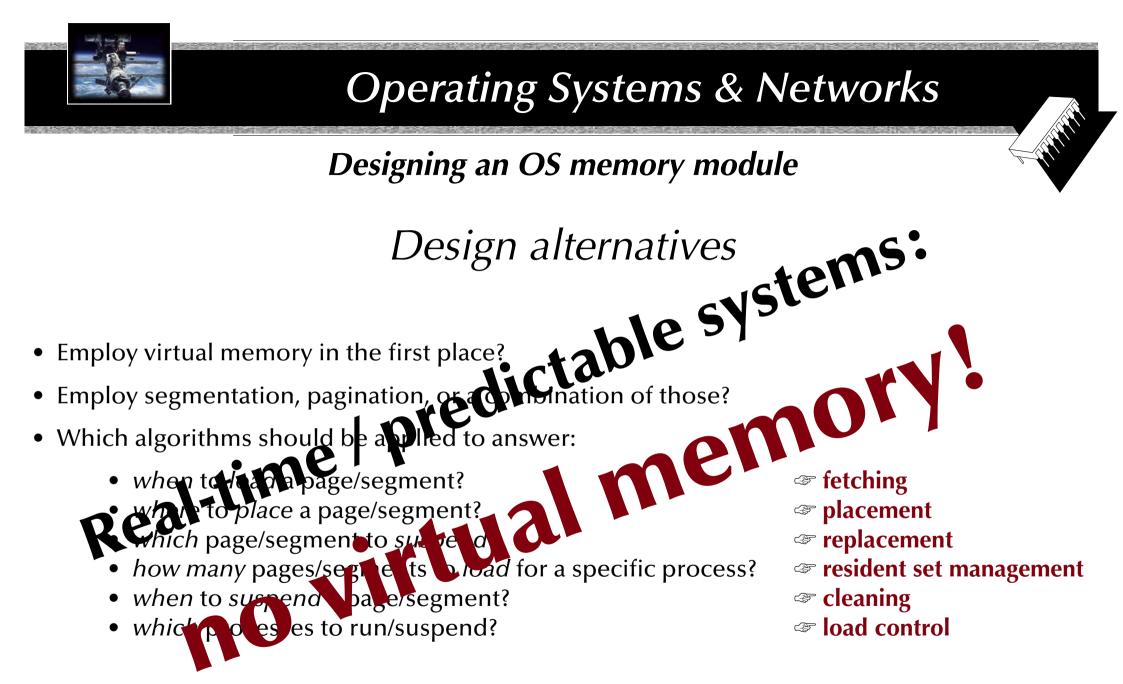

4. Memory

- Requirements & hardware structures

- MMU features & requirements

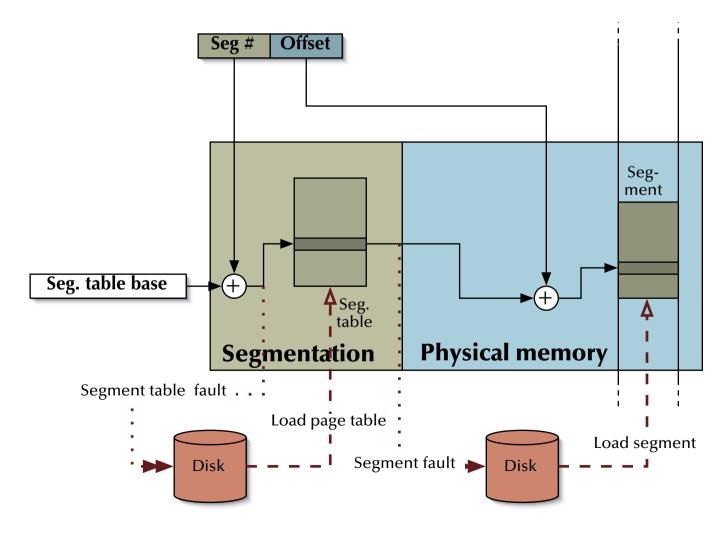

- Partitioning, segmentation, paging & virtual memory

- Simple segmentation

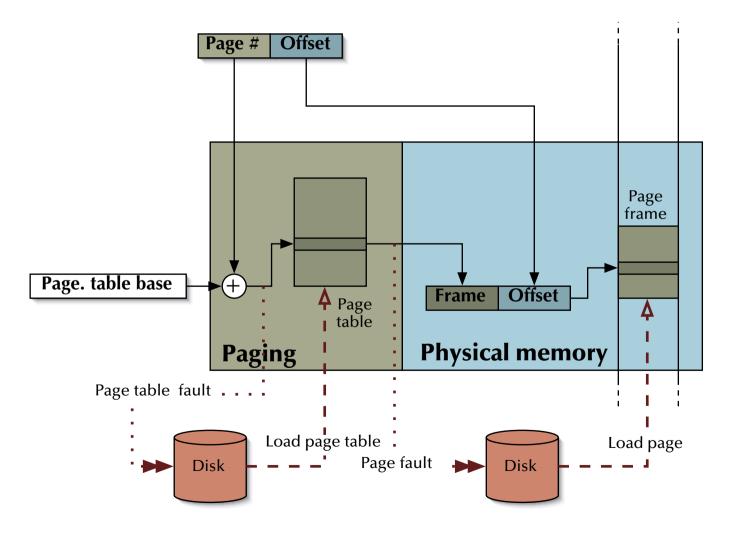

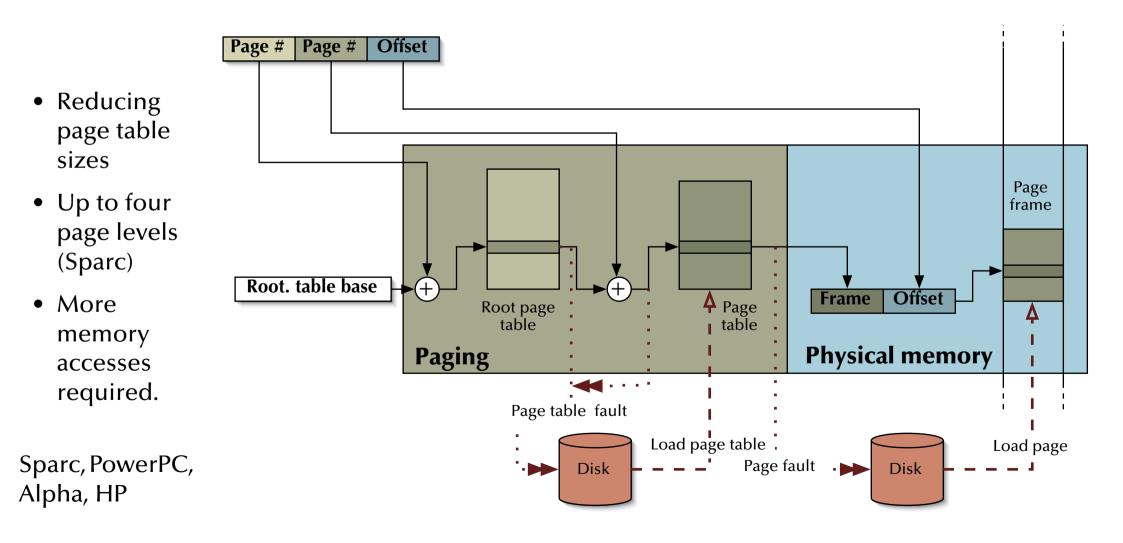

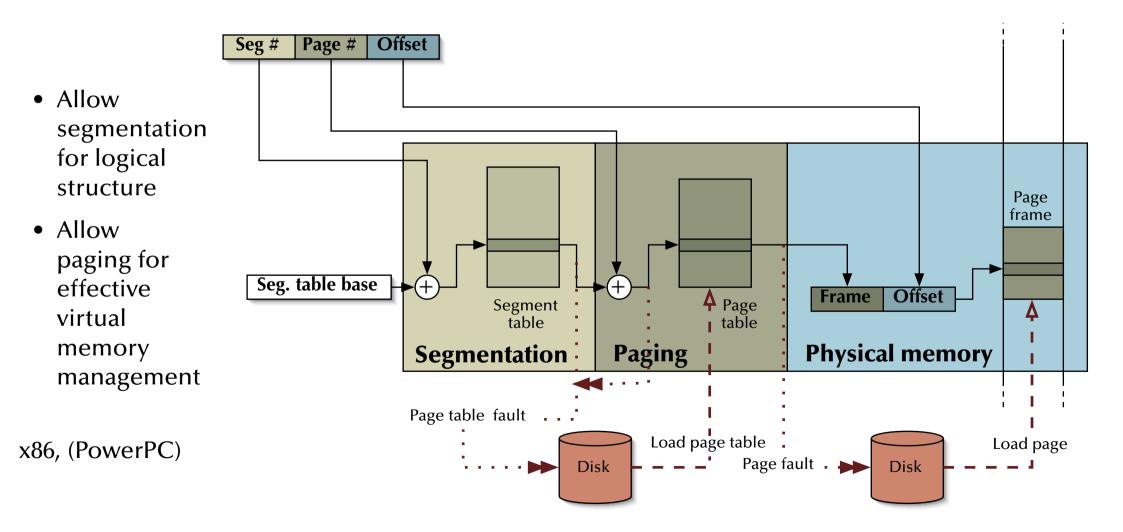

- Simple paging, multi-level paging, combined segmentation & paging

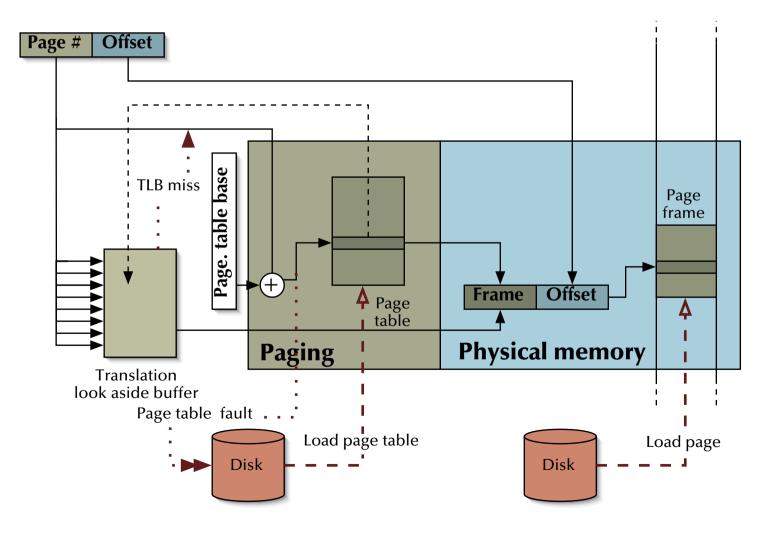

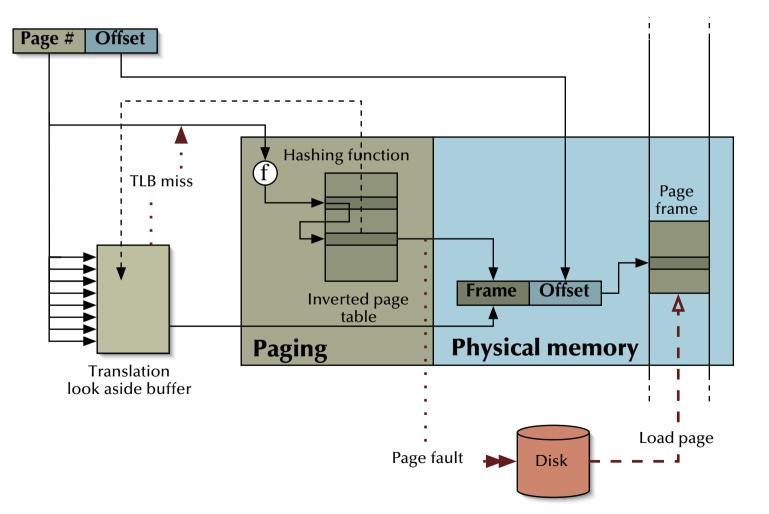

- Translation look aside buffers

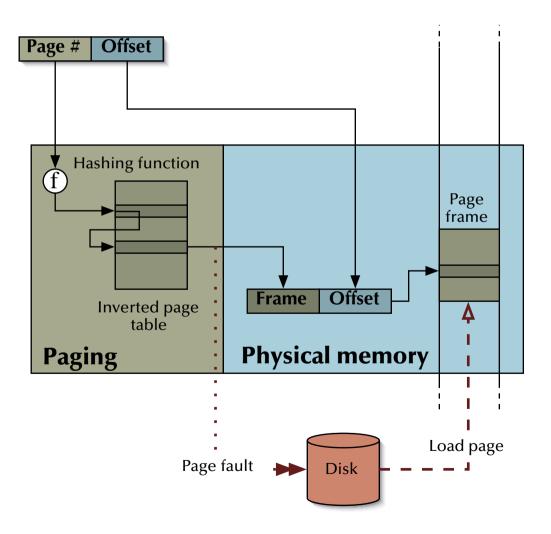

- Hashed tables, Inverted page tables

- Virtual memory management algorithms

- Fetching & placement

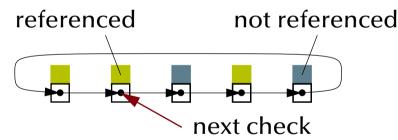

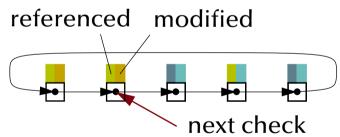

- Replacement

- Resident set management

- Cleaning

- Load control

# Introduction

Uwe R. Zimmer – International University Bremen

#### **References for this chapter**

#### [Silberschatz01]

Abraham Silberschatz, Peter Bear Galvin, Greg Gagne *Operating System Concepts* John Wiley & Sons, Inc., 2001

#### [Stallings2001]

William Stallings *Operating Systems* Prentice Hall, 2001

#### [Tanenbaum97]

Andrew S. Tanenbaum, Albert S. Woodhull *Operating Systems: Design and Implementation* Prentice Hall, 1997

#### [Tanenbaum95]

Andrew S. Tanenbaum Distributed Operating Systems Prentice Hall, 1995

all references and some links are available on the course page

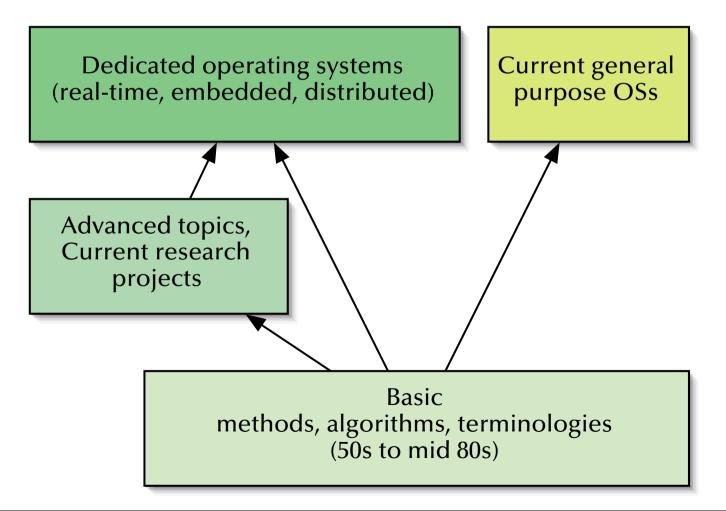

#### What are operating system based on?

#### *Hardware environments / configurations:*

- stand-alone, universal, single-processor machines

- symmetrical multiprocessor-machines

- local distributed systems

- open, web-based systems

- dedicated/embedded computing

# What is the common ground for operating systems?

# What is an operating system?

What is an operating system?

# 1. A virtual machine!

#### ... offering a more comfortable, robust, reliable, flexible ... machine

### What is an operating system?

### 2. A resource manager!

#### ... dealing with all sorts of devices and coordinating access

Operating systems deal with

- processors,

- memory

- mass storage

- communication channels

- devices (timers, special purpose processors, interfaces, ...)

- and many tasks/processes/programs, which are applying for access to these resources

### What is an operating system?

### Is there a standard set of features for an operating system?

☞ no,

the term 'operating systems' covers 4KB kernels, as well as 1GB installations of general purpose OSs.

### Is there a minimal set of features?

#### Imost,

*memory management, process management* and *inter-process communication/synchronization* will be considered essential in most systems.

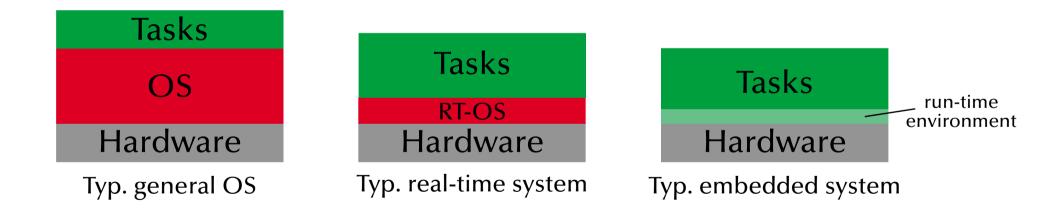

# Is there always an explicit operating system?

⇔ no,

some languages and development systems operate with stand-alone run-time-environments.

#### The evolution of operating systems

- in the beginning: single user, single program, single task, serial processing are no OS

- 50s: System monitors / batch processing

The monitor ordered the sequence of jobs and triggered their sequential execution

- 50s-60s: Advanced system monitors / batch processing:

The monitor is handling interrupts and timers

- are first support for memory protection

- rist implementations of privileged instructions (accessible by the monitor only).

- early 60s: Multiprogramming systems:

employ the long device I/O delays for switches to other, runable programs

- early 60s: Multiprogramming, time-sharing systems:

assign time-slices to each program and switch regularly

- early 70s: Multitasking systems multiple developments resulting in UNIX (besides others)

- early 80s: single user, single tasking systems, with emphasis on user interface (MacOS) or APIs. MS-DOS, CP/M, MacOS and others first employed 'small scale' CPUs (personal computers).

- mid-80s: Distributed/multiprocessor operating systems modern UNIX systems (SYSV, BSD)

#### The evolution of communication systems

- 1901: first wireless data transmission (Morse-code from ships to shore)

- '56: first transmission of data through phone-lines

- '62: first transmission of data via satellites (Telstar)

- '69: ARPA-net (predecessor of the current internet)

- 80s: introduction of fast local networks (LANs): ethernet, token-ring

- 90s: mass introduction of wireless networks (LAN and WAN)

Currently: standard consumer computers come with

- High speed network connectors (e.g. GB-ethernet)

- Wireless LAN (e.g. IEEE802.11)

- Local device bus-system (e.g. firewire)

- Wireless local device network (e.g. bluetooth)

- Infrared communication (e.g. IrDA)

- Modem

#### Types of current operating systems

Personal computing systems and workstations:

- late 70s: Workstations starting by porting UNIX or VMS to 'smaller' computers.

- 80s: PCs starting with almost none of the classical OS-features and services, but with an user-interface (MacOS) and simple device drivers (MS-DOS)

- Iast 20 years: evolving and expanding into current general purpose OSs:

- Solaris (based on SVR4, BSD, and SunOS)

- LINUX (open source UNIX re-implementation for x86 processors and others)

- current Windows (proprietary, partly based on Windows NT, which is 'related' to VMS)

- MacOS X (Mach kernel with BSD Unix and an proprietary user-interface)

- Multiprocessing is supported by all these OSs to some extend.

- None of these OSs is very suitable for embedded systems, also trials have been performed.

- All of these OSs are not suitable at all for distributed or real-time systems.

#### Types of current operating systems

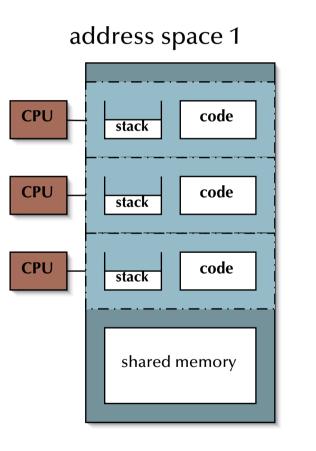

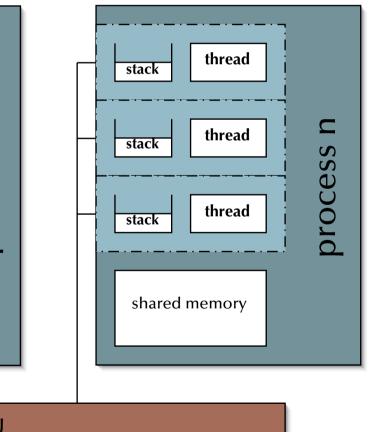

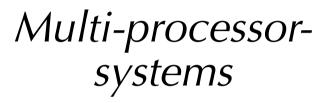

Parallel operating systems

- support for a large number of processors, either:

- symmetrical: each CPU has a full copy of the operating system

- or

- asymmetrical:

only one CPU carries the full operating system,

the others are operated by small operating system stubs to transfer code or tasks.

#### Types of current operating systems

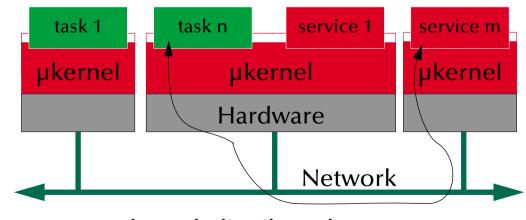

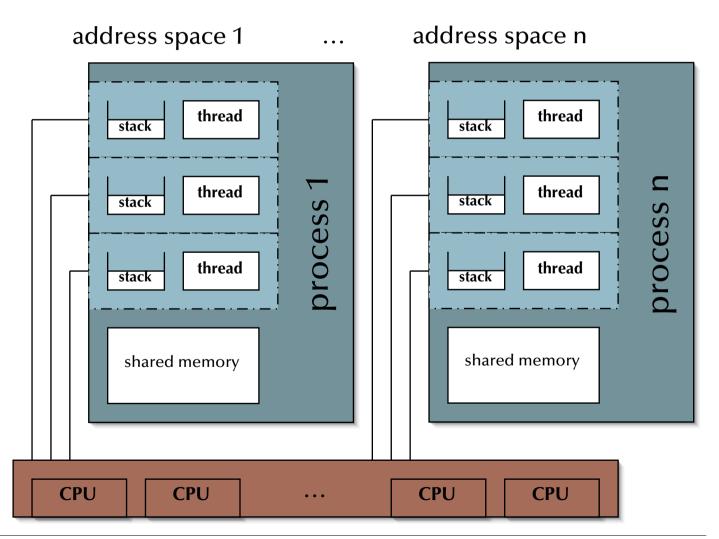

#### Distributed operating systems

- all CPUs carry a small kernel operating system for communication services.

- all other OS-services are distributed over available CPUs

- services may migrate

- services can be multiplied in order to

- guarantee availability (hot stand-by)

- or to increase throughput (heavy duty servers)

#### Types of current operating systems

#### Real-time operating systems

- Fast context switches? *should be fast anyway*

- Small size? ar should be small anyway

- Quick responds to external interrupts? and 'quick', but predictable

- Multitasking? areal time systems are often multitasking systems

- 'low level' programming interfaces? @ needed in many operating systems

- Interprocess communication tools? and needed in almost all operating systems

- High processor utilization? *are fault tolerance builds on redundancy*!

#### Types of current operating systems

Real-time operating systems requesting ...

The logical correctness of the results as well as

the correctness of the time, when the results are delivered

Predictability!

(not performance!)

All results are to be delivered just-in-time – not too early, not too late.

Timing constraints are specified in many different ways ... ... often as a response to 'external' events @ reactive systems

#### Types of current operating systems

#### Embedded operating systems

- usually real-time systems, often hard real-time systems

- very small footprint (often a few KBs)

- none or limited user-interaction

- 90-95% of all processors are working here!

#### Roots of current commercial operating systems

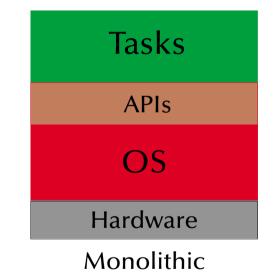

#### Typical structures of operating systems

'Monolithic' or 'the big mess'

- non-portable

- hard to maintain

- lacks reliability

- all services are in the kernel (on the same privilege level)

- may reach very high efficiency

e.g. most early UNIX implementations (70s), MS-DOS (80s), Windows (basically all versions besides NT and NT-based editions), MacOS (until version 9),

#### Typical structures of operating systems

'Monolithic & modular'

- Modules can be platform independent

- Easier to maintain and to develop

- Reliability is increased

- all services are still in the kernel (on the same privilege level)

- may reach very high efficiency

e.g. current LINUX versions

#### Typical structures of operating systems

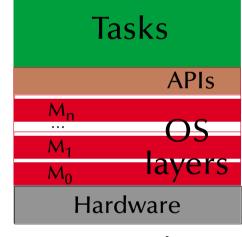

'Monolithic & layered'

- easily portable

- significantly easier to maintain

- crashing layers do not necessarily stop the whole OS

- possibly reduced efficiency through many interfaces

- rigorous implementation of the stacked virtual machine perspective on OSs

Layered

e.g. some current UNIX implementations (e.g. Solaris) to a certain degree, many research OSs (e.g. 'THE system', Dijkstra '68)

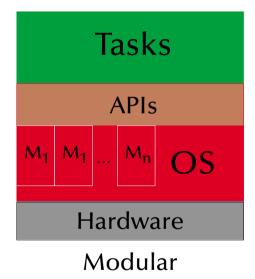

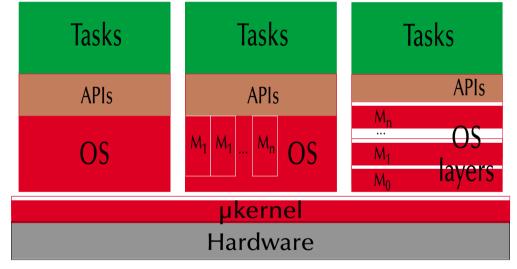

### Typical structures of operating systems

# 'µkernels and virtual machines'

- µkernel implements essential process, memory, and message handling

- all 'higher' services are dealt with outside the kernel @ no threat for the kernel stability

- significantly easier to maintain

- multiple OSs can be executed at the same time

- µkernel is highly hardware dependent

only the µkernel need to be ported.

- possibly reduced efficiency through increased communications

- e.g. wide spread concept: as early as the CP/M, VM/370 ('79) or as recent as MacOS X (mach kernel + BSD unix)

µkernel, virtual machine

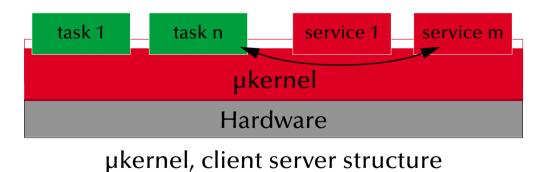

#### Typical structures of operating systems

'µkernels and client-server models'

- µkernel implements essential process, memory, and message handling

- all 'higher' services are user-level servers

- kernel ensures the reliable message passing between clients and servers

- highly modular and flexible

- servers can be redundant and easily replaced

- possibly reduced efficiency through increased communications

e.g. current µkernel research projects

#### Typical structures of operating systems

'µkernels and distributed systems'

- µkernel implements essential process, memory, and message handling

- all 'higher' services are user-level servers

- kernel ensures the reliable message passing between clients and servers: locally and via a communication system

- highly modular and flexible

- servers can be redundant and easily replaced

- possibly reduced efficiency through increased communications

µkernel, distributed systems

#### Basic programming styles

- Imperative (sequential)

- Functional (recursive)

- Declarative (logic)

- Data-flow machines

- (hierarchical) Finite state machines

- Ada, JAVA, Eiffel, C...

- ☞ Lisp, OCaml, …

- ☞ Prolog, …

- ☞ Lustre, Signal, …

- synchronous languages: Esterel, syncEifel, synERJY, ...

### Programming styles alternatives

Imperative  $\leftrightarrow$  Functional  $\leftrightarrow$  Declarative  $\leftrightarrow$  Data-flow  $\leftrightarrow$  Finite state machines Static ↔ Dynamic Modular ↔ Concurrent ↔ Distributed Synchronous ↔ Continuous time Control oriented ↔ Data oriented

### **Programming styles**

What makes a language suitable for operating systems?

- Precise expressions on machine level and address physical memory + I/O

- **Concurrency** rightarrow support for tasking/threading

- **Distribution** receives receives receives a support for message passing or rpc

- **Reliability** and detect errors at compile-time or in the run-time environment

- Large systems = scalable, modular, or object-oriented + separate compilation

- Predictability

ro operations which will lead to unforeseeable timing behaviours (e.g. garbage collection)

#### **Programming styles**

# Languages considered in this course

- C/C++ (for the lab-assignments)

- Ada95 (for your understanding)

- JAVA (for some distribution and object orientated features)

- POSIX (as the IEEE standard for (UNIX-) OS interfaces)

- ... others in places

### Ada95

Ada95 is a **standardized** (ISO/IEC 8652:1995(E)) 'general purpose' language with **core** language primitives for

- strong typing, separate compilation (specification and implementation), object-orientation,

- concurrency, monitors, rpcs, timeouts, scheduling, priority ceiling locks

- strong run-time environments

- ... and **standardized** language-**annexes** for

- additional real-time features, distributed programming, system-level programming, numeric, informations systems, safety and security issues.

### Ada95

## A crash course

- ... refreshing:

- specification and implementation (body) parts, basic types

- exceptions

- information hiding in specifications ('private')

- generic programming

- class-wide programming ('tagged types')

- monitors and synchronisation ('protected', 'entries', 'selects', 'accepts')

- abstract types and dispatching

### Ada95

## Basics

- ... introducing:

- specification and implementation (body) parts

- constants

- some basic types (integer specifics)

- some type attributes

- parameter specification

A simple queue specification

```

package Queue_Pack_Simple is

QueueSize : constant Positive := 10;

type Element is new Positive range 1_000..40_000;

type Marker is mod QueueSize;

type List is array (Marker'Range) of Element;

type Queue_Type is record

Top, Free : Marker := Marker'First;

Elements : List;

end record;

procedure Enqueue (Item: in Element; Queue: in out Queue_Type);

procedure Dequeue (Item: out Element; Queue: in out Queue_Type);

end Queue_Pack_Simple;

```

### A simple queue implementation

```

package body Queue_Pack_Simple is

procedure Engueue (Item: in Element; Queue: in out Queue_Type) is

begin

Queue.Elements (Queue.Free) := Item:

Queue.Free := Queue.Free - 1;

end Enqueue;

procedure Dequeue (Item: out Element; Queue: in out Queue_Type) is

begin

Item

:= Queue.Elements (Queue.Top);

Queue.Top := Queue.Top - 1;

end Dequeue;

end Queue_Pack_Simple;

```

A simple queue test program

with Queue\_Pack\_Simple; use Queue\_Pack\_Simple;

procedure Queue\_Test\_Simple is

```

Queue : Queue_Type;

```

```

Item : Element;

```

```

begin

```

```

Enqueue (2000, Queue);

Dequeue (Item, Queue);

Dequeue (Item, Queue); -- will produce an unpredictable result!

end Queue_Test_Simple;

```

### Ada95

## Exceptions

- ... introducing:

- exception handling

- enumeration types

- functional type attributes

#### A queue specification with proper exceptions

```

package Queue_Pack_Exceptions is

QueueSize : constant Integer := 10;

type Element is (Up, Down, Spin, Turn);

type Marker is mod QueueSize;

type List is array (Marker'Range) of Element;

type Queue_State is (Empty, Filled);

type Queue_Type is record

Top, Free : Marker := Marker'First;

State := Empty;

Elements : List;

end record;

procedure Enqueue (Item: in Element; Queue: in out Queue_Type);

procedure Dequeue (Item: out Element; Queue: in out Queue_Type);

Queueoverflow, Queueunderflow : exception;

```

```

end Queue_Pack_Exceptions;

```

#### A queue implementations with proper exceptions

```

package body Queue_Pack_Exceptions is

procedure Engueue (Item: in Element; Queue: in out Queue_Type) is

begin

if Queue.State = Filled and Queue.Top = Queue.Free then

raise Queueoverflow;

end if:

Queue.Elements (Queue.Free) := Item:

Queue.Free := Marker'Pred (Queue.Free):

Queue.State := Filled;

end Enqueue;

procedure Dequeue (Item: out Element; Queue: in out Queue_Type) is

begin

if Queue.State = Empty then

raise Queueunderflow;

end if:

Item

:= Queue.Elements (Queue.Top);

Queue.Top := Marker'Pred (Queue.Top);

if Queue.Top = Queue.Free then Queue.State := Empty; end if;

end Dequeue;

```

end Queue\_Pack\_Exceptions;

#### A queue test program with proper exceptions

```

with Queue_Pack_Exceptions; use Queue_Pack_Exceptions;

with Ada.Te×t_IO;

use Ada.Te×t_I0;

procedure Queue_Test_Exceptions is

Queue : Queue_Type;

Item : Element;

begin

Enqueue (Turn, Queue);

Dequeue (Item, Queue):

Dequeue (Item, Queue); -- will produce a 'Queue underflow'

exception

when Queueunderflow => Put ("Queue underflow");

=> Put ("Queue overflow");

when Oueueoverflow

end Queue_Test_Exceptions;

```

### Ada95

# Information hiding (private parts)

... introducing:

- private assignments and comparisons are allowed

- limited private entity cannot be assigned or compared

### A queue specification with proper information hiding

```

package Queue_Pack_Private is

QueueSize : constant Integer := 10;

type Element is new Positive range 1...1000;

type Queue_Type is limited private;

procedure Enqueue (Item: in Element; Queue: in out Queue_Type);

procedure Dequeue (Item: out Element; Queue: in out Queue_Type);

Queueoverflow, Queueunderflow : exception;

private

type Marker is mod QueueSize;

type List is array (Marker'Range) of Element;

type Queue_State is (Empty, Filled);

type Queue_Type is record

Top, Free : Marker := Marker'First;

State : Queue_State := Empty;

Elements : List:

end record;

end Queue_Pack_Private:

```

#### A queue implementation with proper information hiding

```

package body Queue_Pack_Private is

procedure Engueue (Item: in Element; Queue: in out Queu _Type) is

begin

if Queue.State = Filled and Queue.Top = Queue Free

the

raise Queueoverflow;

end if;

Queue.Elements (Queue.Free) := Item;

Queue.Free := Queue.Free - 1;

Queue.State := Filled;

end Enqueue;

procedure Dequeue (Item: out Tieme t; Queue: in out Queue_Type) is

begin

if Queue.State = Elota then

raise Queres ler low;

end if;

Item

Queu, Elements (Queue.Top);

Queue.To, := Pureue.Top - 1;

if Queue. p = Queue.Free then Queue.State := Empty; end if;

end Dequeue;

```

© 2003 Uwe R. Zimmer, International University Bremen

end Queue\_Pack\_Private;

### A queue test program with proper information hiding

```

with Oueue_Pack_Private: use Oueue_Pack_Private:

with Ada.Text_IO; use Ada.Text_IO;

procedure Queue_Test_Private is

Queue, Queue_Copy : Queue_Type;

Item

: Element;

begin

Queue_Copy := Queue;

-- compiler-error: left hand of assignment must not be limited type

Enqueue (Item => 1, Queue => Queue);

Dequeue (Item, Queue);

Dequeue (Item, Queue); -- will produce a 'Queue underflow'

exception

when Queueunderflow => Put ("Queue underflow");

=> Put ("Queue overflow");

when Oueueoverflow

end Queue_Test_Private;

```

#### Ada95

## Generic packages

... introducing:

- specification of generic packages

- instantiation of generic packages

A generic queue specification

```

generic

type Element is private;

package Queue_Pack_Generic is

QueueSize: constant Integer := 10;

type Queue_Type is limited private;

procedure Engueue (Item: in Element; Queue: in out Queue_Type);

procedure Dequeue (Item: out Element; Queue: in out Queue_Type);

Queueoverflow, Queueunderflow : exception;

private

type Marker is mod QueueSize;

type List is array (Marker'Range) of Element;

type Queue_State is (Empty, Filled);

type Queue_Type is record

Top, Free : Marker := Marker'First;

State : Queue_State := Empty;

Elements : List;

end record;

end Queue_Pack_Generic:

```

### A generic queue implementation

package body Queue\_Pack\_Generic is

```

procedure Enqueue (Item: in Element; Queue: in out Queu _Type) is

begin

if Queue.State = Filled and Queue.Top = Queue.re

the

raise Queueoverflow:

end if:

Queue.Elements (Queue.Free) := Ltem;

Queue.Free := Queue.Free - 1;

Queue.State := Filled;

end Enqueue;

procedure Dequeue (Item: out Tieme t; Queue: in out Queue_Type) is

begin

if Queue.State = Elota then

raise Que .... Jer low;

end it.

Queu. Elements (Queue.Top);

Item

Queue.To, := Pueue.Top - 1;

if Queue.pp = Queue.Free then Queue.State := Empty; end if;

end Dequeue;

```

end Queue\_Pack\_Generic;

A generic queue test program

```

with Oueue_Pack_Generic:

with Ada.Text_IO;

use Ada.Text_IO;

procedure Queue_Test_Generic is

package Queue_Pack_Positive is

new Queue_Pack_Generic (Element => Positive);

use Queue_Pack_Positive;

Queue : Queue_Type;

Item : Positive;

begin

Enqueue (Item => 1, Queue => Queue);

Dequeue (Item, Queue);

Dequeue (Item, Queue); -- will produce a 'Queue underflow'

exception

when Oueueunderflow

=> Put ("Queue underflow");

when Oueueoverflow

=> Put ("Queue overflow");

end Queue_Test_Generic:

```

© 2003 Uwe R. Zimmer, International University Bremen

### Ada95

# Object oriented programming I

... introducing:

- tagged types are the Ada-way to say that this type can be extended

- derivation of tagged types

- method overwriting

- usage of parent entities

#### An open queue base class specification

```

package Queue_Pack_Object_Base is

QueueSize : constant Integer := 10;

type Element is new Positive range 1..1000;

type Marker is mod QueueSize;

type List is array (Marker'Range) of Element;

type Queue_State is (Empty, Filled);

type Queue_Type is tagged record

Top, Free : Marker := Marker'First;

State := Empty;

Elements : List:

end record;

procedure Enqueue (Item: in Element; Queue: in out Queue_Type);

procedure Dequeue (Item: out Element; Queue: in out Queue_Type);

Queueoverflow, Queueunderflow : exception;

end Queue_Pack_Object_Base;

```

```

© 2003 Uwe R. Zimmer, International University Bremen

```

#### An open queue base class implementation

```

package body Queue_Pack_Object_Base is

procedure Engueue (Item: in Element; Queue: in out Queu _Type) is

begin

if Queue.State = Filled and Queue.Top = Queue Free

the

raise Queueoverflow;

end if;

Queue.Elements (Queue.Free) := Item;

Queue.Free := Queue.Free - 1;

Queue.State := Filled;

end Enqueue;

procedure Dequeue (Item: out Tieme t; Queue: in out Queue_Type) is

begin

if Queue.State = Elota then

raise Queres ler low;

end if;

Item

Queu, Elements (Queue.Top);

Queue.To, := Pureue.Top - 1;

if Queue. p = Queue.Free then Queue.State := Empty; end if;

end Dequeue;

```

```

end Queue_Pack_Object_Base;

```

A derived open queue class specification

with Queue\_Pack\_Object\_Base; use Queue\_Pack\_Object\_Base;

package Queue\_Pack\_Object is

```

type Ext_Queue_Type is new Queue_Type with record

Reader : Marker := Marker'First;

Reader_State : Queue_State := Empty;

end record;

procedure Enqueue (Item: in Element; Queue: in out Ext_Queue_Type);

procedure Read_Queue (Item: out Element; Queue: in out Ext_Queue_Type);

```

end Queue\_Pack\_Object;

A derived open queue class implementation

```

package body Queue_Pack_Object is

procedure Enqueue (Item: in Element; Queue: in out Ext_Queue_Type) is

begin

Enqueue (Item, Queue_Type (Queue));

Queue.Reader_State := Filled;

end Enqueue;

procedure Read_Queue (Item: out Element; Queue: in out Ext_Queue_Type) is

begin

if Queue.Reader_State = Empty then

raise Queueunderflow;

end if:

Item

:= Queue.Elements (Queue.Reader);

Queue.Reader := Queue.Reader - 1;

if Queue.Reader = Queue.Free then Queue.Reader_State := Empty; end if;

end Read_Queue;

```

```

end Queue_Pack_Object;

```

An open class test program

```

with Queue_Pack_Object_Base; use Queue_Pack_Object_Base;

with Queue_Pack_Object; use Queue_Pack_Object;

with Ada.Text_IO;

use Ada.Text_IO;

procedure Queue_Test_Object is

Queue : Ext_Queue_Type;

Item : Element;

begin

Enqueue (Item => 1, Queue => Queue);

Read_Queue (Item, Queue);

Enqueue (Item => 5, Queue => Queue);

Dequeue (Item, Queue);

Dequeue (Item, Queue);

Dequeue (Item, Queue); -- will produce a 'Queue underflow'

exception

when Queueunderflow => Put ("Queue underflow");

=> Put ("Queue overflow");

when Oueueoverflow

end Queue_Test_Object;

```

© 2003 Uwe R. Zimmer, International University Bremen

### Ada95

# Object oriented programming II

- ... introducing:

- private tagged types

- objects which are protected against their children also

#### An encapsulated queue base class specification

```

package Queue_Pack_Object_Base_Private is

QueueSize : constant Integer := 10;

type Element is new Positive range 1..1000;

type Queue_Type is tagged limited private;

procedure Engueue (Item: in Element; Queue: in out Queue_Type);

procedure Dequeue (Item: out Element; Queue: in out Queue_Type);

Queueoverflow, Queueunderflow : exception;

private

type Marker is mod QueueSize;

type List is array (Marker'Range) of Element;

type Queue_State is (Empty, Filled);

type Queue_Type is tagged limited record

Top, Free : Marker := Marker'First;

State : Queue_State := Empty;

Elements : List;

end record;

```

end Queue\_Pack\_Object\_Base\_Private;

#### An encapsulated queue base class implementation

```

package body Queue_Pack_Object_Base_Private is

procedure Engueue (Item: in Element; Queue: in out Queu _Type) is

begin

if Queue.State = Filled and Queue.Top = Queue Free

the

raise Queueoverflow;

end if;

Queue.Elements (Queue.Free) := Item;

Queue.Free := Queue.Free - 1;

Queue.State := Filled;

end Enqueue;

procedure Dequeue (Item: out Tieme t; Queue: in out Queue_Type) is

begin

if Queue.State = Elota then

raise Queres ler low;

end if;

Item

Queu, Elements (Queue.Top);

Queue.To, := Pureue.Top - 1;

if Queue. p = Queue.Free then Queue.State := Empty; end if;

end Dequeue;

```

```

end Queue_Pack_Object_Base_Private;

```

A derived encapsulated queue class specification

with Queue\_Pack\_Object\_Base\_Private; use Queue\_Pack\_Object\_Base\_Private; package Queue\_Pack\_Object\_Private is

type Ext\_Queue\_Type is new Queue\_Type with private; subtype Depth\_Type is Positive range 1..QueueSize;

procedure Look\_Ahead (Item: out Element;

Depth: in Depth\_Type; Queue: in out Ext\_Queue\_Type);

private

type Ext\_Queue\_Type is new Queue\_Type with null record;

end Queue\_Pack\_Object\_Private;

A derived encapsulated queue class implementation

```

package body Queue_Pack_Object_Private is

procedure Look_Ahead (Item: out Element;

Depth: in Depth_Type; Queue: in out Ext_Queue_Type) is

Storage : Queue_Type;

ShuffleItem : Element;

begin

for I in 1..Depth - 1 loop

Dequeue (ShuffleItem, Queue);

Enqueue (ShuffleItem, Storage);

end loop;

Dequeue (Item, Queue);

Engueue (Item, Storage);

(...)

```

```

(...)

Read_The_Rest:

begin

for I in 1..QueueSize - Depth loop

Dequeue (ShuffleItem, Queue);

Enqueue (ShuffleItem, Storage);

end loop;

exception

when Queueunderflow => null; -- rect he rest is done

end Read_The_Rest;

Restore_The_Oueue:

begin

for I in 1..Queue, ze hop

Dequeue (Shuffle).em,

to go ar

Enqueue (Shufflelem, Lieue);

end loop;

exception

when Queueunderflow => null; -- restore is done

end Restore_The_Queue;

end Look_Ahead;

end Queue_Pack_Object_Private;

```

#### An encapsulated class test program

```

with Queue_Pack_Object_Base_Private; use Queue_Pack_Object_Base_Private;

with Queue_Pack_Object_Private;

use Queue_Pack_Object_Private;

with Ada.Te×t_IO;

use Ada.Text_IO;

procedure Queue_Test_Object_Private is

Queue : Ext_Queue_Type;

Item : Element;

begin

Enqueue (Item => 1, Queue => Queue);

Enqueue (Item => 1, Queue => Queue);

Look_Ahead (Item => Item, Depth => 2, Queue => Queue);

Enqueue (Item => 5, Queue => Queue);

Dequeue (Item, Queue);

Dequeue (Item, Queue);

Dequeue (Item, Queue);

Dequeue (Item, Queue); -- will produce a 'Queue underflow'

exception

when Queueunderflow => Put ("Queue underflow");

when Oueueoverflow

=> Put ("Queue overflow");

end Queue_Test_Object_Private;

```

© 2003 Uwe R. Zimmer, International University Bremen

### Ada95

### Tasks & Monitors

- ... introducing:

- protected types

- tasks (definition, instantiation and termination)

- task synchronisation

- entry guards

- entry calls

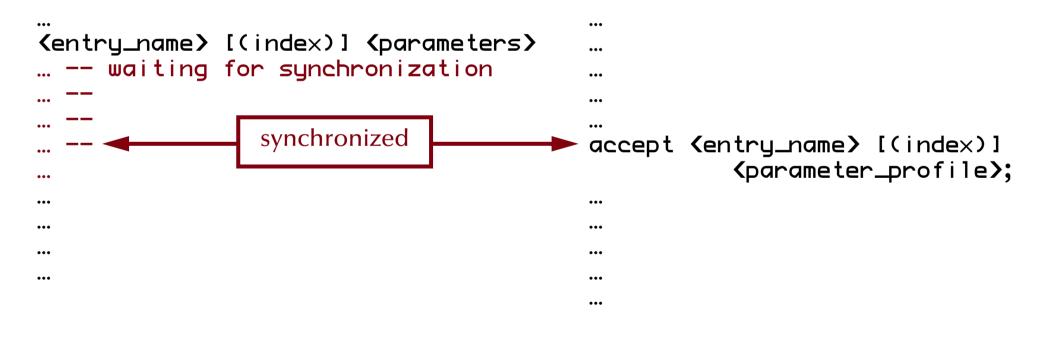

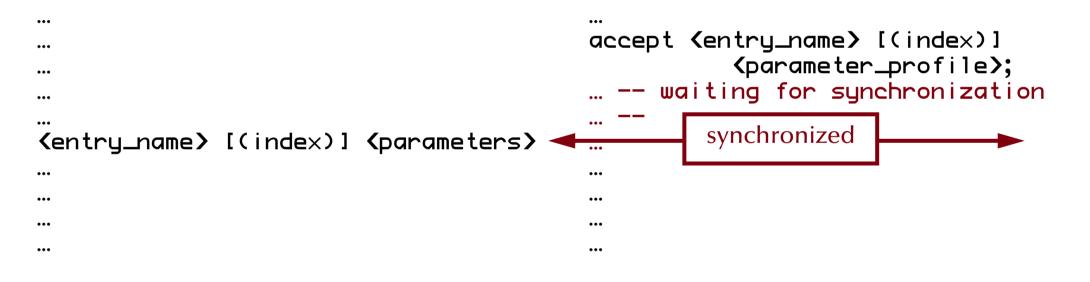

- accept and selected accept statements

#### A protected queue specification

```

Package Queue_Pack_Protected is

QueueSize : constant Integer := 10;

subtupe Element is Character:

type Queue_Type is limited private;

Protected type Protected_Queue is

entry Engueue (Item: in Element);

entry Dequeue (Item: out Element);

private

Queue : Queue_Type;

end Protected_Queue:

private

type Marker is mod QueueSize;

type List is array (Marker'Range) of Element;

type Queue_State is (Empty, Filled);

type Queue_Type is record

Top, Free : Marker := Marker'First;

State : Queue_State := Empty;

Elements : List;

end record;

end Queue_Pack_Protected:

```

### A protected queue implementation

```

package body Queue_Pack_Protected is

protected body Protected_Queue is

entry Engueue (Item: in Element) when

Queue.State = Empty or Queue.Top /= Queue.Free is

begin

Queue.Elements (Queue.Free) := Item;

Queue.Free := Queue.Free - 1;

Queue.State := Filled;

end Enqueue;

entry Dequeue (Item: out Element) when

Oueue.State = Filled is

begin

:= Queue.Elements (Queue.Top);

Item

Queue.Top := Queue.Top - 1;

if Queue.Top = Queue.Free then Queue.State := Empty; end if;

end Dequeue;

end Protected_Queue;

```

end Queue\_Pack\_Protected;

#### A multitasking protected queue test program

```

with Queue_Pack_Protected; use Queue_Pack_Protected;

with Ada.Text_IO:

use Ada.Text_I0;

procedure Queue_Test_Protected is

Queue : Protected_Queue;

task Producer is entry shutdown; end Producer;

task Consumer is

end Consumer;

task body Producer is

Item : Element;

Got_It : Boolean;

begin

select

accept shutdown; exit; -- main task loop

else

Get_Immediate (Item, Got_It);

if Got_It then

Queue.Enqueue (Item); -- task might be blocked here!

else

delay 0.1; --sec.

end if;

end select;

end loop;

end Producer;

(...)

```

A multitasking protected queue test program (cont.)

```

(...)

task body Consumer is

Item : Element;

begin

100p

Queue.Dequeue (Item); -- task might be blocked here!

Put ("Received: "); Put (Item); Put_Line ("!");

if Item = 'a' then

Put___ine ("Shutting down producer"); Producer.Shutdown;

Put_line ("Shutting down consumer"); exit; -- main task loop

end if;

end loop;

end Consumer;

begin

null;

end Queue_Test_Protected:

```

#### Ada95

# Abstract types & dispatching

- ... introducing:

- abstract tagged types

- abstract subroutines

- concrete implementation of abstract types

- dispatching to different packages, tasks, and partitions according to concrete types

#### An abstract queue specification

```

package Queue_Pack_Abstract is

subtype Element is Character;

type Queue_Type is abstract tagged limited private;

procedure Enqueue (Item: in Element; Queue: in out Queue_Type) is

abstract;

procedure Dequeue (Item: out Element; Queue: in out Queue_Type) is

abstract;

```

private

type Queue\_Type is abstract tagged limited null record; end Queue\_Pack\_Abstract;

A concrete queue specification

```

with Queue_Pack_Abstract; use Queue_Pack_Abstract;

package Queue_Pack_Concrete is

QueueSize : constant Integer := 10;

type Real_Queue is new Queue_Type with private;

procedure Enqueue (Item: in Element; Queue: in out Real_Queue);

procedure Dequeue (Item: out Element; Queue: in out Real_Queue);

Queueoverflow, Queueunderflow : exception;

private

type Marker is mod QueueSize:

type List is array (Marker'Range) of Element;

type Queue_State is (Empty, Filled);

type Real_Queue is new Queue_Type with record

Top, Free : Marker := Marker'First;

State : Queue_State := Empty;

Elements : List:

end record;

end Queue_Pack_Concrete:

```

© 2003 Uwe R. Zimmer, International University Bremen

#### A concrete queue implementation

```

package body Queue_Pack_Concrete is

procedure Engueue (Item: in Element; Queue: in out Real_Queue) is

begin

if Queue.State = Filled and Queue.Top = Queue.Free then

raise Queueoverflow;

end if;

Queue.Elements (Queue.Free) := Item;

Queue.Free := Queue.Free - 1;

Queue.State := Filled;

end Enqueue;

procedure Dequeue (Item: out Element; Queue: in out Real_Queue) is

begin

if Queue.State = Empty then

raise Queueunderflow;

end if:

:= Queue.Elements (Queue.Top);

Item

Queue.Top := Queue.Top - 1;

if Queue.Top = Queue.Free then Queue.State := Empty; end if;

end Dequeue;

```

end Queue\_Pack\_Concrete;

### A multitasking dispatching test program

```

with Queue_Pack_Abstract; use Queue_Pack_Abstract;

with Queue_Pack_Concrete; use Queue_Pack_Concrete;

```

```

procedure Queue_Test_Dispatching is

```

```

type Queue_Class is access all Queue_Type'class;

```

```

task Queue_Holder is -- could be on an individual partition

entry Queue_Filled;

end Queue_Holder;

```

```

task Queue_User is -- could be on an individual partition

entry Send_Queue (Remote_Queue: in Queue_Class);

end Queue_User;

```

```

(...)

```

```

task body Queue_Holder is

Local_Queue : Queue_Class;

Item : Element;

begin

Local_Queue := new Real_Queue; -- could be a different implementation!

Queue_User.Send_Queue (Local_Queue);

accept Queue_Filled do

Dequeue (Item, Local_Queue.all); -- Item will be 'r'

end Queue_Filled:

end Queue_Holder;

task body Queue_User is

Local_Queue : Queue_Class;

Item : Element;

begin

Local_Queue := new Real_Queue; -- could be a different implementation!

accept Send_Queue (Remote_Queue: in Queue_Class) do

Enqueue ('r', Remote_Queue.all); -- potentially a rpc!

Enqueue ('1', Local_Queue.all);

end Send_Queue;

Queue_Holder.Queue_Filled;

Dequeue (Item, Local_Queue.all); -- Item will be 'l'

end Queue_User;

```

begin null; end Queue\_Test\_Dispatching;

#### Ada95

## Ada95 language status

- Established language standard with free and commercial compilers available for all major OSs.

- Stand-alone runtime environments for embedded systems (some are only available commercially).

- Special (yet non-standard) extensions (i.e. language reductions and proof systems) for extreme small footprint embedded systems or high integrity real-time environments available are Ravenscar profile systems.

- has been used and is in use in numberless large scale projects

(e.g. in the international space station, and in some spectacular crashes: e.g. Ariane 5)

#### POSIX

Portable Operating System Interface for Computing Environments

- IEEE/ANSI Std 1003.1 and following

- Program Interface (API) [C Language]

- more than 30 different POSIX standards

(a system is 'POSIX compliant', if it implements parts of just one of them!)

#### **POSIX** – some of the real-time relevant standards

| 1003.1<br>12/01  | OS Definition                       | single process, multi process, job control, signals, user groups, file system, file attributes, file device management, file locking, device I/O, device-specific control, system database, pipes, FIFO,                        |

|------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

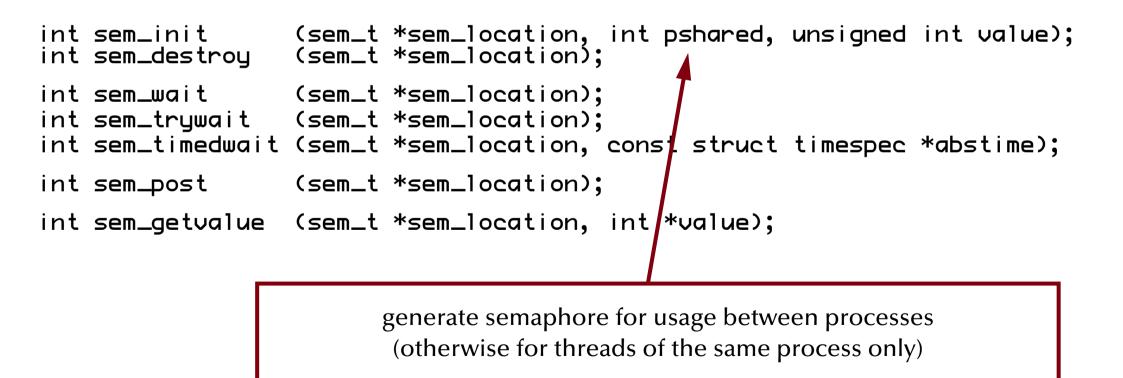

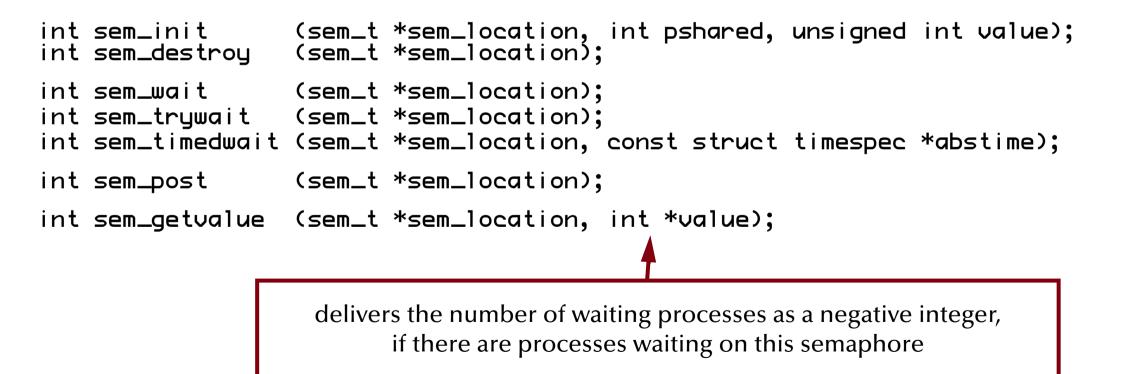

| 1003.1b<br>10/93 | Real-time<br>Extensions             | real-time signals, priority scheduling, timers, asynchronous I/O, prioritized I/O, synchronized I/O, file sync, mapped files, memory locking, memory protection, message passing, sema-<br>phore,                               |

| 1003.1c<br>6/95  | Threads                             | multiple threads within a process; includes support for: thread control, thread attributes, pri-<br>ority scheduling, mutexes, mutex priority inheritance, mutex priority ceiling, and condition<br>variables                   |

| 1003.1d<br>10/99 | Additional Real-<br>time Extensions | new process create semantics (spawn), sporadic server scheduling, execution time monitor-<br>ing of processes and threads, I/O advisory information, timeouts on blocking functions, de-<br>vice control, and interrupt control |

| 1003.1j<br>1/00  | Advanced Real-<br>time Extensions   | typed memory, nanosleep improvements, barrier synchronization, reader/writer locks, spin<br>locks, and persistent notification for message queues                                                                               |

| 1003.21<br>-/-   | Distributed<br>Real-time            | buffer management, send control blocks, asynchronous and synchronous operations, bounded blocking, message priorities, message labels, and implementation protocols                                                             |

### *POSIX – 1003.1b*

Frequently employed POSIX features include:

- **Timers:** delivery is accomplished using POSIX signals

- **Priority scheduling:** fixed priority, 32 priority levels

- **Real-time signals:** signals with multiple levels of priority

- **Semaphore:** named semaphore

- Memory queues: message passing using named queues

- Shared memory: memory regions shared between multiple processes

- Memory locking: no virtual memory swapping of physical memory pages

#### **POSIX** – support in some OSs

|                 | POSIX 1003.1<br>(Base POSIX)                 | POSIX 1003.1b<br>(Real-time<br>extensions)           | POSIX 1003.1c<br>(Threads)               |

|-----------------|----------------------------------------------|------------------------------------------------------|------------------------------------------|

| Solaris         | Full support                                 | Full support                                         | Full support                             |

| IRIX            | Conformant                                   | Full support                                         | Full support                             |

| LynxOS          | Conformant                                   | Full support                                         | Conformant (Version 3.1)                 |

| QNX<br>Neutrino | Full support                                 | Partial support<br>(no memory locking)               | Full support                             |

| Linux           | Full support                                 | Partial support<br>(no timers,<br>no message queues) | Full support                             |

| VxWorks         | Partial support<br>(different process model) | Partial support<br>(different process model)         | Supported through third<br>party product |

**POSIX** – other languages

### POSIX is a 'C' standard ...

#### ... but **bindings to other languages** are also (suggested) POSIX standards:

- Ada: 1003.5\*, 1003.24 (some PAR approved only, some withdrawn)

- Fortran: 1003.9 (6/92)

- Fortran90: 1003.19 (withdrawn)

- ... and there are POSIX standards for task-specific POSIX profiles, e.g.:

- Super computing: 1003.10 (6/95)

- Realtime: 1003.13, 1003.13b (3/98)

- profiles 51-54: combinations of the above RT-relevant POSIX standards @ RT-Linux

- Embedded Systems: 1003.13a (PAR approved only)

**POSIX** – example: setting a timer

```

void timer_create(int num_secs, int num_nsecs)

struct sigaction sa;

struct sigevent sig_spec;

sigset_t allsigs;

struct itimerspec tmr_setting;

timer_t timer_h;

/* setup signal to respond to timer */

sigemptyset(&sa.sa_mask);

sa.sa_flags = SA_SIGINF0;

sa.sa_sigaction = timer_intr;

if (sigaction(SIGRTMIN, &sa, NULL) < 0)

perror('sigaction');

sig_spec.sigev_notify = SIGEV_SIGNAL;

sig_spec.sigev_signo = SIGRTMIN;

```

}

}

### **Operating Systems & Networks**

```

POSIX – example: setting a timer (cont.)

```

```

/* create timer, which uses the REALTIME clock */

íf (timer_creaté(CLOCK_REALTIME, &sig_spec, &timer_h) < 0)

perror('timer create');

/* set the initial expiration and frequency of timer */

tmr_setting.it_value.tv_sec = 1;

tmr_setting.it_value.tv_nsec = 0;

tmr_setting.it_interval.tv_sec = num_secs;

tmr_setting.it_interval.tv_sec = num_nsecs;

if ( timer_settime(timer_h, 0, &tmr_setting,NULL) < 0)

perror('settimer');

/* wait for signals */

sigemptyset(&allsigs);

while (1) {

sigsuspend(&allsigs);

}

/* routine that is called when timer expires */

void timer_intr(int sig, siginfo_t *extra, void *cruft)

/* perform periodic processing and then exit */

```

}

ł

}

### **Operating Systems & Networks**

```

POSIX – example: setting a timer (cont.)

```

```

/* create timer, which uses the REALTIME clock */

íf (timer_creaté(CLOCK_REALTIME, &sig_spec, &timer_h) < 0)

perror('timer create');

/* set the initial expiration and frequency of timer */

tmr_setting.it_value.tv_sec = 1;

tmr_setting.it_value.tv_nsec = 0;

tmr_setting.it_interval.tv_sec = num_secs;

tmr_setting.it_interval.tv_sec = num_nsecs;

remember the Pearl timers?

sigsuspend(&alls AFTER 30 MIN ALL 5 MIN DURING 1 HRS ACTIVATE Help;

if ( timer_settime(timer_h, 0, &tmr_setting,NULL)

/* wait for signals */

sigemptyset(&allsigs)*

while (1) {

}

/* routine that is called when timer expires */

void timer_intr(int sig, siginfo_t *extra, void *cruft)

/* perform periodic processing and then exit */

```

#### Languages

### Languages used in this course

|                                      | Ada                                | RT-Java   | C/C++                              | Posix                       |

|--------------------------------------|------------------------------------|-----------|------------------------------------|-----------------------------|

| Predictability                       | ***<br>(specific<br>run-time env.) | <br>(OOP) | implementation<br>dependent        | implementation<br>dependent |

| low-level interfaces                 | * * *                              | -         | **                                 | * *                         |

| Concurrency                          | ***                                | **        |                                    | * *                         |

| Distribution                         | **                                 | * * *     |                                    | *                           |

| Error detection<br>(compiler, tools) | **<br>(strong typing)              | **        |                                    |                             |

| Large systems                        | ***                                | * * *     | OOP C++ style<br>(no support in C) | /                           |

© 2003 Uwe R. Zimmer, International University Bremen

Page 88 of 432 (chapter 1: to 89)

#### Summary

### Introduction to operating systems

- Features (and non-features) of operating system

- Common grounds for operating systems

- Historical perspectives

- Types of current operating systems

- Design principles for system software (monoliths & µkernels)

- Examples of languages considered for system level programming:

- Java

- Ada95

- POSIX interfaces

- C/C++

### Hardware Fundamentals

Uwe R. Zimmer – International University Bremen

#### **References for this chapter**

#### [Silberschatz01] – Chapter 2

Abraham Silberschatz, Peter Bear Galvin, Greg Gagne *Operating System Concepts* John Wiley & Sons, Inc., 2001 [Stallings2001] – Chapter 1 William Stallings

*Operating Systems* Prentice Hall, 2001

#### all references and some links are available on the course page

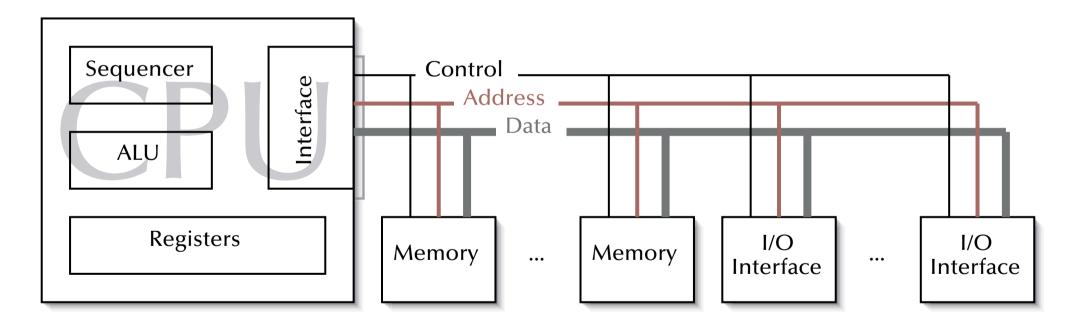

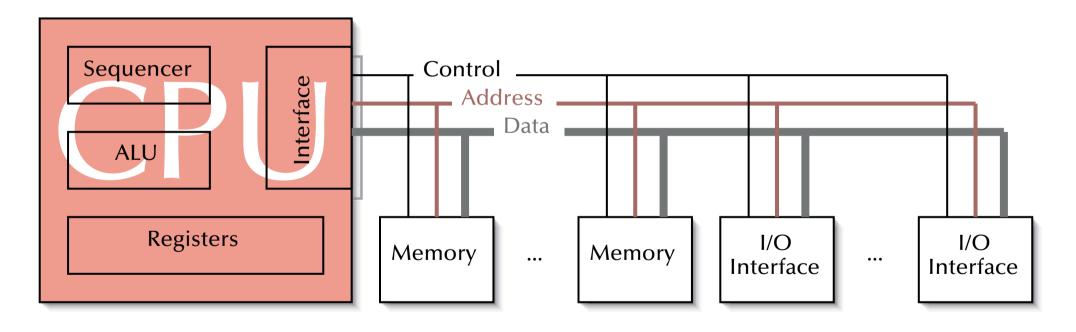

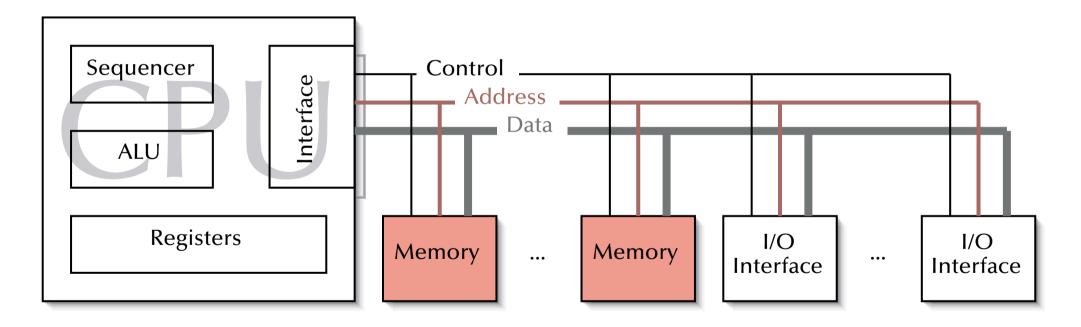

### Hardware Fundamentals

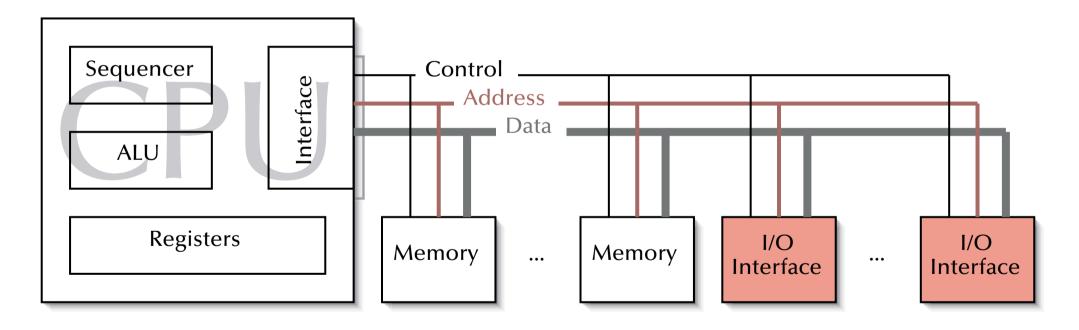

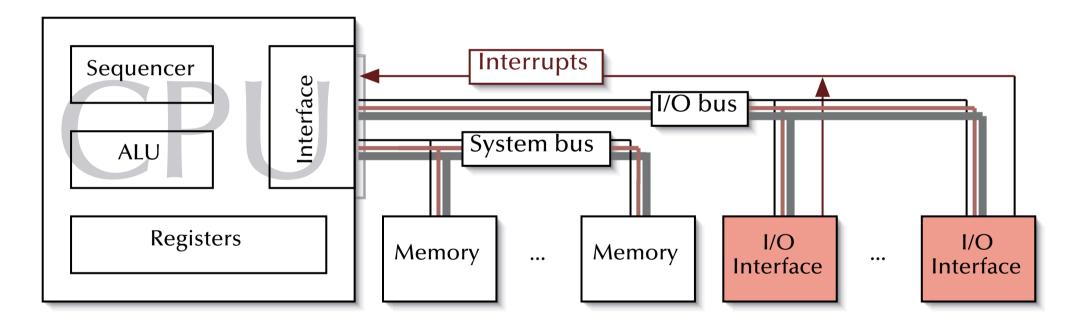

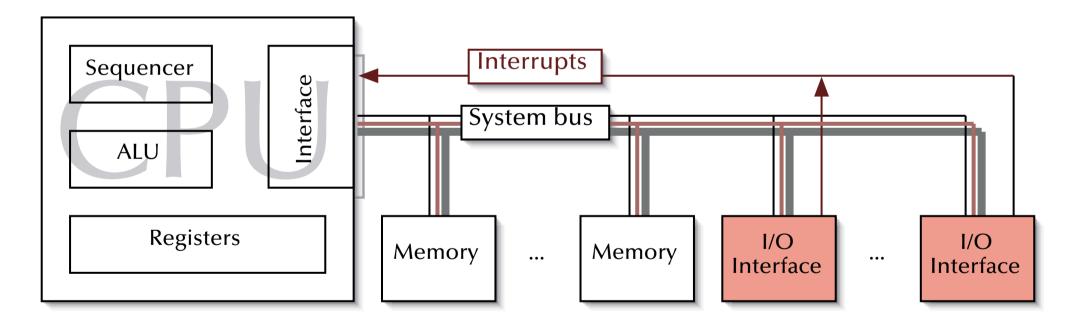

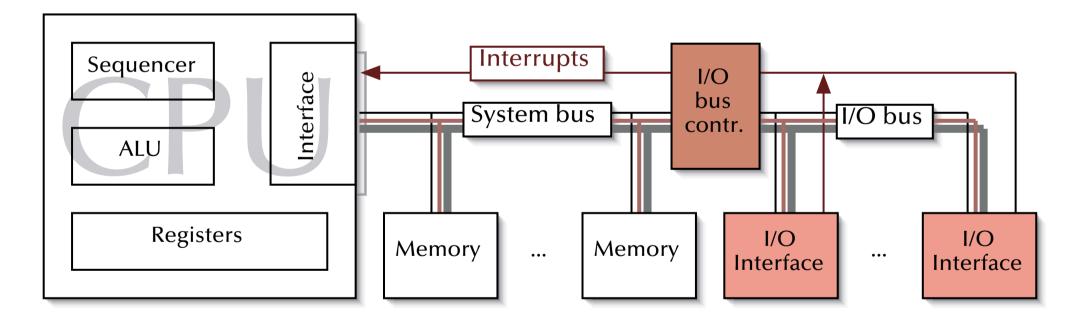

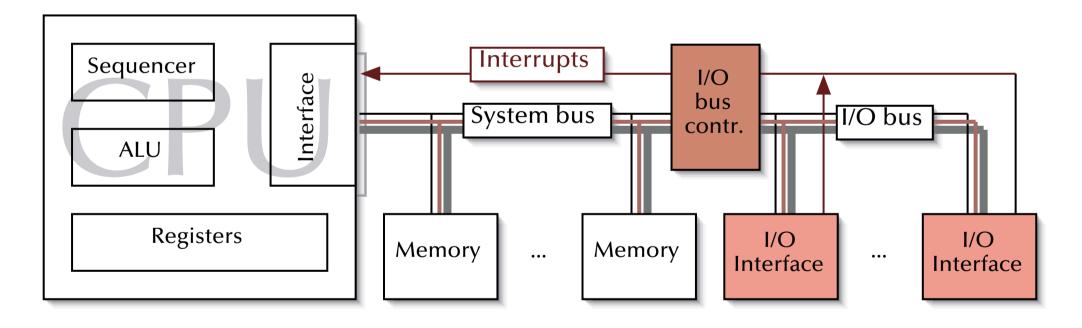

### A common computer architecture:

- Bus-systems carry device, address information and data (8-64bit wide) as well as control lines in groups such as:

- arbitration, synchronization, requests, interrupts, priorities

### Hardware Fundamentals

### The CPU

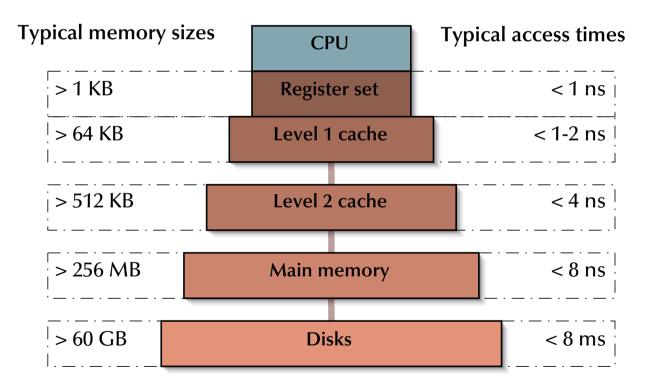

- CPU components relevant for this course:

- register-set, sequencer ('normal operation'), interrupt controller, protected modes

#### Hardware Fundamentals

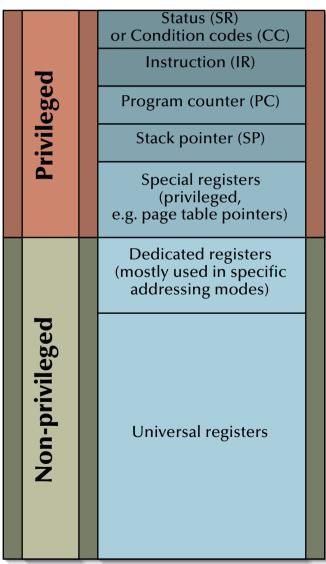

### Register set

- SR: Status / Condition codes (CC), e.g.: privilege level, interrupt level, result of last operation

- IR: current instruction

- PC: Address of current (next) instruction

- SP: Top of stack address

- Special privileged registers, e.g.: page table entries, memory protection maps

- Dedicated registers, e.g.: registers which can by employed in some contexts only

- Universal registers: registers, which can be employed for any purpose (addressing, storage, index, parameters, ...)

#### **Register structure**

| Status (SR)<br>or Condition codes (CC)                               |

|----------------------------------------------------------------------|

| Instruction (IR)                                                     |

| Program counter (PC)                                                 |

| Stack pointer (SP)                                                   |

| Special registers<br>(privileged,<br>e.g. page table pointers)       |

| Dedicated registers<br>(mostly used in specific<br>addressing modes) |

| Universal registers                                                  |

#### Hardware Fundamentals

Register set

- Often divided into a privileged and non-privileged section

- Switch from non-privileged to privileged mode only via traps or interrupts (later in this chapter)

- IR, PC, SP

+ some general registers (or at least one 'accumulator') are found in all current processor designs

• Special and dedicated registers are not used in all architectures

#### **Register structure**

#### Hardware Fundamentals

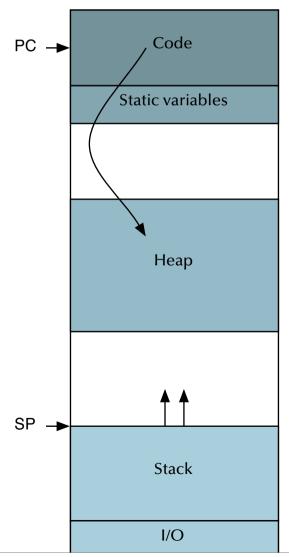

Main memory layout

Memory layout

- Classical usage of the RAM areas in most processors

- Main storage of data in

- heap

- stack

- or local static

depends on the usage of the programming language

$\ensuremath{\mathbb{C}}$  2003 Uwe R. Zimmer, International University Bremen

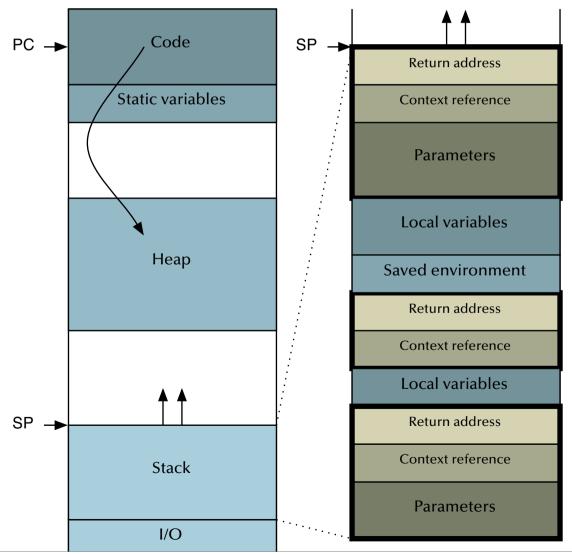

#### Hardware Fundamentals

Main memory layout

Stack frames

- Every sub-program call leaves an entry on the stack with all relevant information:

- parameters

- context (not in 'C')

- return address

- Parameters may be removed by:

- the calling routine ('C')

- or the called routine

- Special architectures support faster parameter passing (e.g. register-bands)

© 2003 Uwe R. Zimmer, International University Bremen

Page 97 of 432 (chapter 2: to 157)

### Hardware Fundamentals

# Privileged instructions

#### Purpose:

- prevent user level tasks from by-passing the operating system

- restrict access form user-level tasks to resources, which are managed by the operating system:

- Memory

- I/O

- Structures which are used to administer memory or I/O access (e.g. special registers, MMUs, etc.)

#### Implementation:

- declare some instructions privileged

- implement two (or more) protection levels in the CPU

- allow changes to a higher privilege level by means of traps/exceptions/interrupts only.

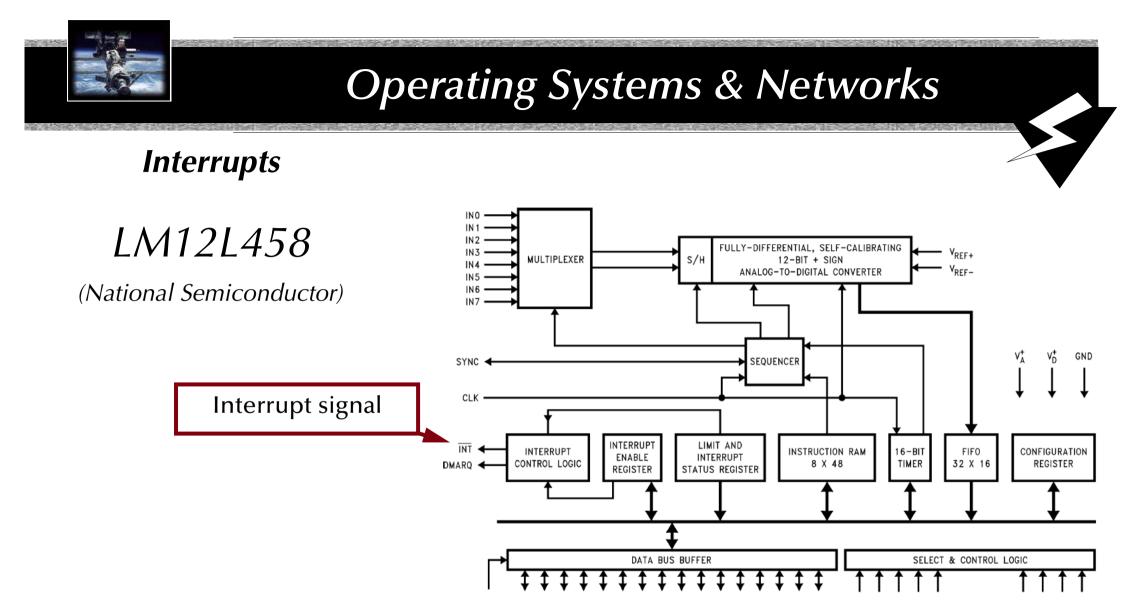

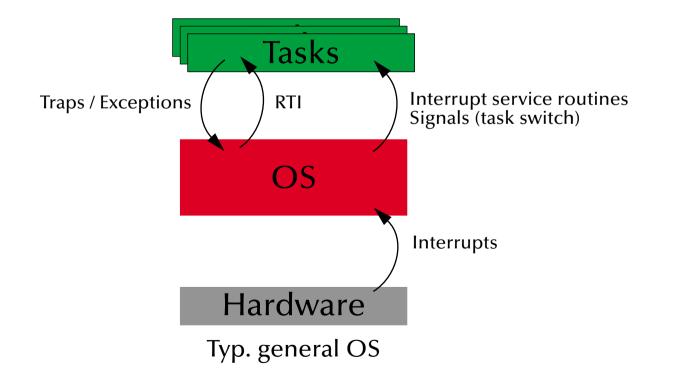

### Asynchronism

Interrupts

Required mechanisms for interrupt driven programming:

- Interrupt control: grouping, encoding, prioritising, and en-/disabling interrupt sources

- **Context switching**: mechanisms for cpu-state saving and restoring + task-switching

- Interrupt identification: Interrupt vectors, interrupt states

#### hardware-supported

### Asynchronism

Interrupts

#### **Interrupt control**:

- ... at the individual device level

- ... at the system interrupt controller level

- ... at the operating system level

- beyond task-level (interrupt service routines)

- communicating interrupts to task

- transforming interrupts to signals

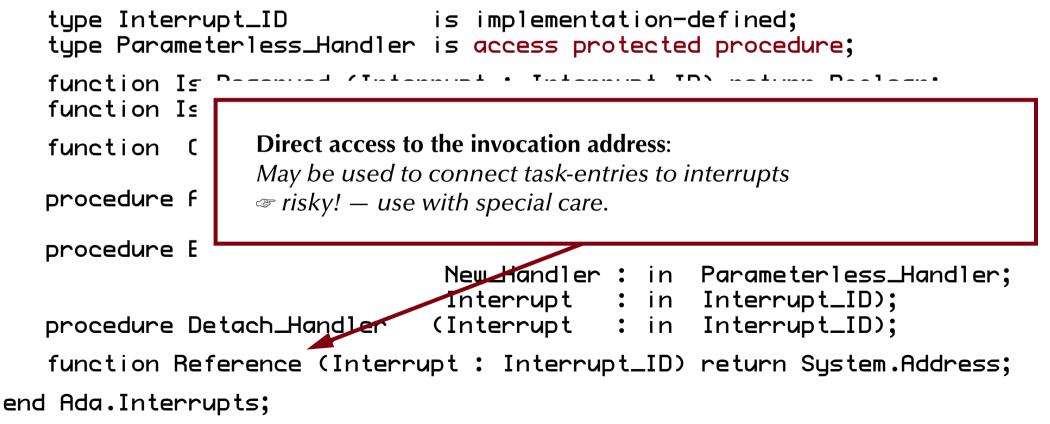

### ... at the language level

#### only one interrupt signal line available!

real in order to identify the interrupt reason, an additional read cycle is required!

### A/D, D/A & Interfaces

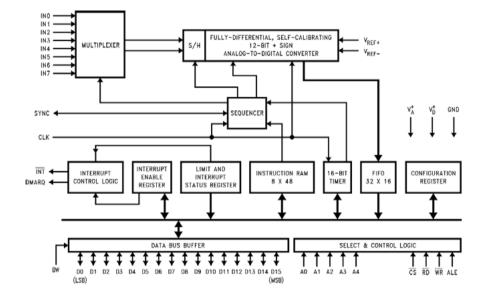

#### LM12L458 12-Bit + sign, 8 channel, A/D converter, controller and interface

#### **Controller features**:

- Programmable acquisition times and conversion rates

- 32-word conversion FIFO

- Self-calibration and diagnostic mode

- 8- or 16-bit wide data bus microprocessor or DSP

Typ. applications:

- Data Logging

- Process Control

### LM12L458 – accessible registers

| A4 | A3 | A2 | A1 | Purpose            | Туре | D15 | D14 D13     | D12      | D11            | D10      | D9        | D8   | D7    | D6                 | D5    | D4       | D3               | D2    | D1    | D0    |

|----|----|----|----|--------------------|------|-----|-------------|----------|----------------|----------|-----------|------|-------|--------------------|-------|----------|------------------|-------|-------|-------|

|    | 0  | 0  | 0  | Instruction RAM    | R/W  |     | Acquisition |          | Watch-         |          |           |      |       | •                  | •     |          | •                | •     |       |       |

| 0  |    | to |    | (RAM Pointer = 00) |      |     | Time        |          | dog            | 8/12     | Timer     | Sync |       | $V_{IN-}$          |       |          | V <sub>IN+</sub> |       | Pause | Loop  |

|    | 1  | 1  | 1  |                    |      |     |             |          |                |          |           |      |       |                    |       |          |                  |       |       |       |

|    | 0  | 0  | 0  | Instruction RAM    | R/W  |     |             |          |                | •        |           |      |       |                    |       |          |                  |       |       |       |

| 0  |    | to |    | (RAM Pointer = 01) |      |     | I           | Don't C  | are            |          | >/<       | Sign |       |                    |       | Lim      | it #1            |       |       |       |

|    | 1  | 1  | 1  |                    |      |     |             |          |                |          |           |      |       |                    |       |          |                  |       |       |       |

|    | 0  | 0  | 0  | Instruction RAM    | R/W  |     |             |          |                |          |           |      |       |                    |       |          |                  |       |       | ,     |

| 0  |    | to |    | (RAM Pointer = 10) |      |     | I           | Don't C  | are            |          | >/<       | Sign |       |                    |       | Lim      | it #2            |       |       |       |

|    | 1  | 1  | 1  |                    |      |     |             |          |                |          |           |      |       |                    |       |          |                  |       |       |       |

| 1  | 0  | 0  | 0  | Configuration      | R/W  |     |             |          | DIAG           | Test     | RA        | ٩M   | 1/0   | Auto               | Chan  | Stand-   | Full             | Auto- | Reset | Start |

|    |    |    |    | Register           |      |     | Don't Care  |          | DIAG           | = 0      | Poi       | nter | Sel   | Zero <sub>ec</sub> | Mask  | by       | CAL              | Zero  |       |       |

|    |    |    |    | Interrupt Enable   | R/W  |     | Number of   | Conve    | ersions        | s        | equenc    | er   | INT7  | Don't              | INT5  | INT4     | INT3             | INT2  | INT1  | INT0  |

| 1  | 0  | 0  | 1  | Register           |      |     | in Conve    | FIFO     | A              | ddress   | to        |      | Care  |                    |       |          |                  |       |       |       |

|    |    |    |    |                    |      |     | to Gene     | erate II | NT2            | Gei      | nerate I  | NT1  |       |                    |       |          |                  |       |       |       |

|    |    |    |    |                    |      |     |             |          |                |          | Address   | s    |       |                    |       |          |                  |       |       |       |

|    |    |    |    |                    | R    |     | Actual      | Numbe    | r of           |          | of        |      | INST7 | "0"                | INST5 | INST4    | INST3            | INST2 | INST1 | INSTO |

| 1  | 0  | 1  | 0  | Interrupt Status   |      |     | Convers     | ion Re   | sults          | s        | equenc    | er   |       |                    |       |          |                  |       |       |       |

|    |    |    |    | Register           |      |     | in Conve    | ersion I | FIFO           | 1        | nstructio | on   |       |                    |       |          |                  |       |       |       |

|    |    |    |    |                    |      |     |             |          |                |          | being     |      |       |                    |       |          |                  |       |       |       |

|    |    |    |    |                    |      |     |             |          |                | 6        | Execute   | d    |       |                    |       |          |                  |       |       |       |

| 1  | 0  | 1  | 1  | Timer              | R/W  |     |             | Timer    | Preset High    | Byte     |           |      |       | I                  | Tim   | her Pres | et Low E         | Byte  |       | 1     |

|    |    |    |    | Register           |      |     |             |          |                |          |           |      |       |                    |       |          |                  |       |       |       |

| 1  | 1  | 0  | 0  | Conversion         | R    | A   | ddress      | Sign     | (              | Convers  | ion       |      |       |                    | Cor   | version  | Data: L          | SBs   |       |       |

|    |    |    |    | FIFO               |      | c   | or Sign     |          | C              | Data: MS | SBs       |      |       |                    |       |          |                  |       |       |       |

| 1  | 1  | 0  | 1  | Limit Status       | R    |     |             | Li       | nit #2: Status | S        |           |      |       |                    |       | Limit #1 | : Status         | ;     |       |       |

|    |    |    |    | Register           |      |     |             |          |                |          |           |      |       |                    |       |          |                  |       |       |       |

### LM12L458 – instruction RAM

| A4 | A3 | A2 | A1 | Purpose            | Туре | D15 | D14        | D13      | D12 | D11    | D10  | D9    | D8   | D7 | D6        | D5 | D4  | D3        | D2 | D1    | D0   |

|----|----|----|----|--------------------|------|-----|------------|----------|-----|--------|------|-------|------|----|-----------|----|-----|-----------|----|-------|------|

|    | 0  | 0  | 0  | Instruction RAM    | R/W  |     | Acqu       | uisition |     | Watch- |      |       |      |    |           |    |     |           |    |       |      |

| 0  |    | to |    | (RAM Pointer = 00) |      |     | Ti         | ime      |     | dog    | 8/12 | Timer | Sync |    | $V_{IN-}$ |    |     | $V_{IN+}$ |    | Pause | Loop |

|    | 1  | 1  | 1  |                    |      |     |            |          |     |        |      |       |      |    |           |    |     |           |    |       |      |

|    | 0  | 0  | 0  | Instruction RAM    | R/W  |     |            |          |     |        |      |       |      |    |           |    |     |           |    |       |      |

| 0  |    | to |    | (RAM Pointer = 01) |      |     | Don't Care |          |     |        |      |       | Sign |    |           |    | Lim | it #1     |    |       |      |

|    | 1  | 1  | 1  |                    |      |     |            |          |     |        |      |       |      |    |           |    |     |           |    |       |      |

|    | 0  | 0  | 0  | Instruction RAM    | R/W  |     |            |          |     |        |      |       |      |    |           |    |     |           |    |       |      |

| 0  |    | to |    | (RAM Pointer = 10) |      |     | Don't Care |          |     |        |      |       | Sign |    |           |    | Lim | it #2     |    |       |      |

|    | 1  | 1  | 1  |                    |      |     |            |          |     |        |      |       |      |    |           |    |     |           |    |       |      |

#### every entry in the **instruction RAM** consists of:

- **Loop** (1bit): indicates the last instruction and branches to the first one.

- **Pause** (1bit): halts the sequencer before this instruction.

- $V_{IN+}$ ,  $V_{IN-}$  (2\*3bit): select the input channels (000 selects ground in  $V_{IN-}$ )

- Sync (1bit): wait for an external sync. signal before this instruction.

- Timer (1bit): wait for a preset 16-bit counter delay before this instruction.

### LM12L458 – instruction RAM

| A4 | A3 | A2 | A1 | Purpose            | Туре | D15        | D14  | D13      | D12     | D11    | D10  | D9    | D8   | D7 | D6        | D5 | D4  | D3        | D2 | D1    | D0   |

|----|----|----|----|--------------------|------|------------|------|----------|---------|--------|------|-------|------|----|-----------|----|-----|-----------|----|-------|------|

|    | 0  | 0  | 0  | Instruction RAM    | R/W  |            | Acqu | uisition |         | Watch- |      |       |      |    |           | -  |     |           |    |       |      |

| 0  |    | to |    | (RAM Pointer = 00) |      |            | Т    | ime      |         | dog    | 8/12 | Timer | Sync |    | $V_{IN-}$ |    |     | $V_{IN+}$ |    | Pause | Loop |

|    | 1  | 1  | 1  |                    |      |            |      |          |         |        |      |       |      |    |           |    |     |           |    |       |      |

|    | 0  | 0  | 0  | Instruction RAM    | R/W  |            |      |          |         |        |      |       |      |    |           |    |     |           |    |       |      |

| 0  |    | to |    | (RAM Pointer = 01) |      |            |      | [        | Don't C | are    |      | >/<   | Sign |    |           |    | Lim | t #1      |    |       |      |

|    | 1  | 1  | 1  |                    |      |            |      |          |         |        |      |       |      |    |           |    |     |           |    |       |      |

|    | 0  | 0  | 0  | Instruction RAM    | R/W  |            |      |          |         |        |      |       |      |    |           |    |     |           |    |       |      |

| 0  |    | to |    | (RAM Pointer = 10) |      | Don't Care |      |          |         |        |      | >/<   | Sign |    |           |    | Lim | t #2      |    |       |      |

|    | 1  | 1  | 1  |                    |      |            |      |          |         |        |      |       |      |    |           |    |     |           |    |       |      |

#### every entry in the **instruction RAM** consists of (cont.):

- 8/12 (1bit): selects the resolution (8 bit + sign or 12 bit + sign).

- Watchdog (1 bit): activates comparisons with two programmed limits.

- Acquisition time (D) (4bit): the converter takes 9 + 2D cycles (12bit mode) or 2 + 2D cycles (8bit mode) to sample to input. Depends on the input resistance:  $D \approx 0.45 \cdot R_S[k\Omega] \cdot f_{CLK}[MHz]$  for 12 bit conversions.

- Limits (including sign and comparator): used for Watchdog operation.

### LM12L458 – instruction RAM

| A4 | 1 / | A3 | A2 | A1 | Purpose            | Туре | D15 | D14  | D13     | D12 | D11    | D10   | D9   | D8 | D7        | D6 | D5 | D4        | D3 | D2    | D1   | D0 |

|----|-----|----|----|----|--------------------|------|-----|------|---------|-----|--------|-------|------|----|-----------|----|----|-----------|----|-------|------|----|

|    |     | 0  | 0  | 0  | Instruction RAM    | R/W  |     | Acqu | isition |     | Watch- |       |      |    |           |    |    |           |    |       |      |    |

| 0  |     |    | to |    | (RAM Pointer = 00) |      |     | Time |         | dog | 8/12   | Timer | Sync |    | $V_{IN-}$ |    |    | $V_{IN+}$ |    | Pause | Loop |    |

|    |     | 1  | 1  | 1  |                    |      |     |      |         |     |        |       |      |    |           |    |    |           |    |       |      |    |

type ChannelPlus is (Ch0, Ch1, Ch2, Ch3, Ch4, Ch5, Ch6, Ch7); type ChannelMinus is (Gnd, Ch1, Ch2, Ch3, Ch4, Ch5, Ch6, Ch7); type Resolutions is (TwelveBit, EightBit); type Aquisition\_D is new Integer range 0..15; -- 9+2D (12bit), 2+2D (8bit) for ChannelPlus use (Ch0 => 0, Ch1 => 1, Ch2 => 2, Ch3 => 3, Ch4 = > 4, Ch5 = > 5, Ch6 = > 6, Ch7 = > 7; for ChannelMinus use (Gnd => 0, Ch1 => 1, Ch2 => 2, Ch3 => 3, Ch4 = 4, Ch5 = 5, Ch6 = 6, Ch7 = 7; for Resolutions use (TwelveBit => 0, EightBit => 1); tupe Instruction is record EndOfLoop, Pause, Sync, Timer, Watchdog : Boolean; : ChannelPlus; Vplus Uminus : ChannelMinus: **Resolution** : Resolutions; : Aquisition\_D; AquisitionTime end record;

© 2003 Uwe R. Zimmer, International University Bremen

### LM12L458 – instruction RAM

| A | 4 | A3 | A2 | A1 | Purpose            | Туре | D15 | D14  | D13     | D12 | D11    | D10   | D9   | D8 | D7        | D6 | D5 | D4        | D3 | D2    | D1   | D0 |

|---|---|----|----|----|--------------------|------|-----|------|---------|-----|--------|-------|------|----|-----------|----|----|-----------|----|-------|------|----|

|   |   | 0  | 0  | 0  | Instruction RAM    | R/W  |     | Acqu | isition |     | Watch- |       |      |    |           |    |    |           |    |       |      |    |

| ( | ) |    | to |    | (RAM Pointer = 00) |      |     | Time |         | dog | 8/12   | Timer | Sync |    | $V_{IN-}$ |    |    | $V_{IN+}$ |    | Pause | Loop |    |

|   |   | 1  | 1  | 1  |                    |      |     |      |         |     |        |       |      |    |           |    |    |           |    |       |      |    |

Units\_Per\_Word : constant Integer := Word\_Size / Storage\_Unit;

#### for Instruction use record

| End0fLoop      | at | 0*Units_Per_Word range | 00;   |

|----------------|----|------------------------|-------|

| Pause          | at | 0*Units_Per_Word range | 1 1;  |

| Vplus          | at | 0*Units_Per_Word range | 24;   |

| Vminus         | at | 0*Units_Per_Word range | 5 7;  |

| Sync           | at | 0*Units_Per_Word range | 8 8;  |

| Timer          | at | 0*Units_Per_Word range | 99;   |

| Resolution     | at | 0*Units_Per_Word range | 1010; |

| Watchdog       | at | 0*Units_Per_Word range | 1111; |

| AquisitionTime | at | 0*Units_Per_Word range | 1215; |

| end record;    |    |                        |       |

© 2003 Uwe R. Zimmer, International University Bremen

### LM12L458 – instruction RAM

| A | 1 | A3 | A2 | A1 | Purpose            | Туре | D15 | D14  | D13     | D12 | D11    | D10   | D9   | D8 | D7        | D6 | D5 | D4        | D3 | D2    | D1   | D0 |

|---|---|----|----|----|--------------------|------|-----|------|---------|-----|--------|-------|------|----|-----------|----|----|-----------|----|-------|------|----|

|   |   | 0  | 0  | 0  | Instruction RAM    | R/W  |     | Acqu | isition |     | Watch- |       |      |    |           |    |    |           |    |       |      |    |

| 0 |   |    | to |    | (RAM Pointer = 00) |      |     | Time |         | dog | 8/12   | Timer | Sync |    | $V_{IN-}$ |    |    | $V_{IN+}$ |    | Pause | Loop |    |

|   |   | 1  | 1  | 1  |                    |      |     |      |         |     |        |       |      |    |           |    |    |           |    |       |      |    |

- for Instruction'Size use 16; -- Bits

for Instruction'Alignment use 2; -- Storage\_Units (Bytes)

for Instruction'Bit\_Order use High\_Order\_First;

- type Instructions is array (0..7) of Instruction;

pragma Pack (Instructions);

- ADC\_Instructions : Instructions;

- for ADC\_Instructions'Address use To\_Address (16#0000132D#);

### LM12L458 – instruction RAM

| A | 4 | A3 | A2 | A1 | Purpose            | Туре | D15 | D14  | D13     | D12 | D11    | D10  | D9    | D8   | D7 | D6        | D5 | D4 | D3        | D2 | D1    | D0   |

|---|---|----|----|----|--------------------|------|-----|------|---------|-----|--------|------|-------|------|----|-----------|----|----|-----------|----|-------|------|

|   |   | 0  | 0  | 0  | Instruction RAM    | R/W  |     | Acqu | isition |     | Watch- |      |       |      |    |           |    |    |           |    |       |      |

| 0 |   |    | to |    | (RAM Pointer = 00) |      |     | Ti   | me      |     | dog    | 8/12 | Timer | Sync |    | $V_{IN-}$ |    |    | $V_{IN+}$ |    | Pause | Loop |

|   |   | 1  | 1  | 1  |                    |      |     |      |         |     |        |      |       |      |    |           |    |    |           |    |       |      |

| ADC_Instructions | (0) := | Pause<br>Vplus<br>Vminus<br>Sync<br>Timer<br>Resolution | <pre>=&gt; False,<br/>=&gt; False,<br/>=&gt; Ch0,<br/>=&gt; Gnd,<br/>=&gt; True,<br/>=&gt; False,<br/>=&gt; False,<br/>=&gt; False,<br/>=&gt; 10);</pre> |

|------------------|--------|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADC_Instructions | (1) := | Pause<br>Vplus<br>Vminus<br>Sync<br>Timer<br>Resolution | => False,                                                                                                                                                |

## LM12L458 – instruction RAM

| A4 | . / | 43 | A2 | A1 | Purpose            | Туре | D15 | D14  | D13     | D12 | D11    | D10  | D9    | D8   | D7 | D6        | D5 | D4 | D3        | D2 | D1    | D0   |

|----|-----|----|----|----|--------------------|------|-----|------|---------|-----|--------|------|-------|------|----|-----------|----|----|-----------|----|-------|------|

|    |     | 0  | 0  | 0  | Instruction RAM    | R/W  |     | Acqu | isition |     | Watch- |      |       |      |    |           |    |    |           |    |       |      |

| 0  |     |    | to |    | (RAM Pointer = 00) |      |     | Tir  | me      |     | dog    | 8/12 | Timer | Sync |    | $V_{IN-}$ |    |    | $V_{IN+}$ |    | Pause | Loop |

|    |     | 1  | 1  | 1  |                    |      |     |      |         |     |        |      |       |      |    |           |    |    |           |    |       |      |

### Data structures in 'C':

### enum ChannelPlus {Ch0=0, Ch1, Ch2, Ch3, Ch4, Ch5, Ch6, Ch7}; enum ChannelMinus {Gnd=0, Ch1, Ch2, Ch3, Ch4, Ch5, Ch6, Ch7}; enum Resolutions {TwelveBit=0, EightBit};

### struct {

| unsigned int EndOfLoop      | • | 1; |

|-----------------------------|---|----|

| unsigned int Pause          |   | 1; |

| ChannelPlus Vplus           | • | 3; |

| ChannelMinus Vininus        | • | 3; |

| unsigned int Sync           | • | 1; |

| unsigned int Timer          | • | 1; |

| Resolutions Resolution      | • | 1; |

| unsigned int Watchdog       | • | 1; |

| unsigned int AquisitionTime | • | 4; |

| Instruction;                |   |    |

## LM12L458 – instruction RAM

| A | A3 | A2 | A1 | Purpose            | Туре | D15 | D14  | D13     | D12 | D11    | D10  | D9    | D8   | D7 | D6        | D5 | D4 | D3        | D2 | D1    | D0   |

|---|----|----|----|--------------------|------|-----|------|---------|-----|--------|------|-------|------|----|-----------|----|----|-----------|----|-------|------|

|   | 0  | 0  | 0  | Instruction RAM    | R/W  |     | Acqu | isition |     | Watch- |      |       |      |    |           |    |    |           |    |       |      |

| 0 |    | to |    | (RAM Pointer = 00) |      |     | Ti   | me      |     | dog    | 8/12 | Timer | Sync |    | $V_{IN-}$ |    |    | $V_{IN+}$ |    | Pause | Loop |

|   | 1  | 1  | 1  |                    |      |     |      |         |     |        |      |       |      |    |           |    |    |           |    |       |      |

## Data structures in 'C':

```

struct {

unsigned int EndOfLoop

unsigned int Pause

1;

3;

3;

1;

ChannelPlus Vplus

ChannelMinus Uminus

unsigned int Sync

1;

1;

1;

unsigned int Timer

Resolutions Resolution

unsigned int Watchdog

unsigned int AquisitionTime

4:

} Instruction;

Instruction InstructionsA[8];

InstructionsA *Instructions:

Instructions = 0 \times 0000132D;

```

### LM12L458 – instruction RAM

| A | 4 | A3 | A2 | <b>A</b> 1 | Purpose            | Туре | D15 | D14  | D13     | D12 | D11    | D10  | D9    | D8   | D7 | D6        | D5 | D4 | D3        | D2 | D1    | D0   |

|---|---|----|----|------------|--------------------|------|-----|------|---------|-----|--------|------|-------|------|----|-----------|----|----|-----------|----|-------|------|

|   |   | 0  | 0  | 0          | Instruction RAM    | R/W  |     | Acqu | isition |     | Watch- |      |       |      |    |           |    |    |           |    |       |      |

|   | ) |    | to |            | (RAM Pointer = 00) |      |     | Ti   | me      |     | dog    | 8/12 | Timer | Sync |    | $V_{IN-}$ |    |    | $V_{IN+}$ |    | Pause | Loop |

|   |   | 1  | 1  | 1          |                    |      |     |      |         |     |        |      |       |      |    |           |    |    |           |    |       |      |

Data structures in 'C':